全体概要

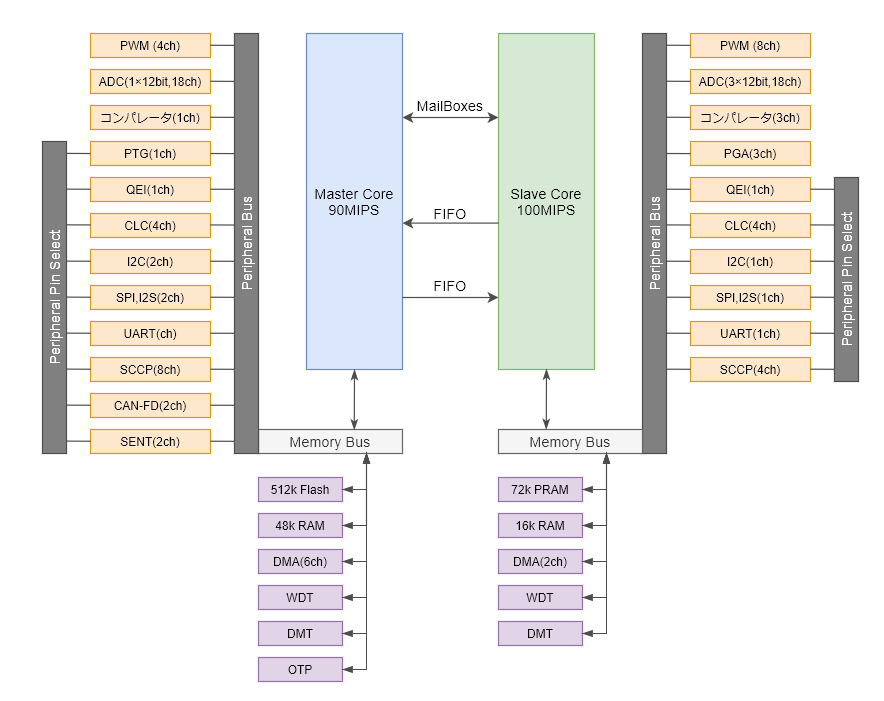

dsPIC33CHデュアルコアファミリーはその名の通り1チップ内にCPUコアが2つ内蔵され、高性能デジタル電源やモータ制御等がメインターゲットとなっております。またメインコアでユーザーインターフェースや通信やシステム監視等を主に、スレーブコアでクリティカルな制御コードを実行出来る様なペリフェラルの割り付けとなっています。

メインコアは90MIPS、スレーブコアは100MIPSで動作し全体で190MIPSの処理速度を有しています。

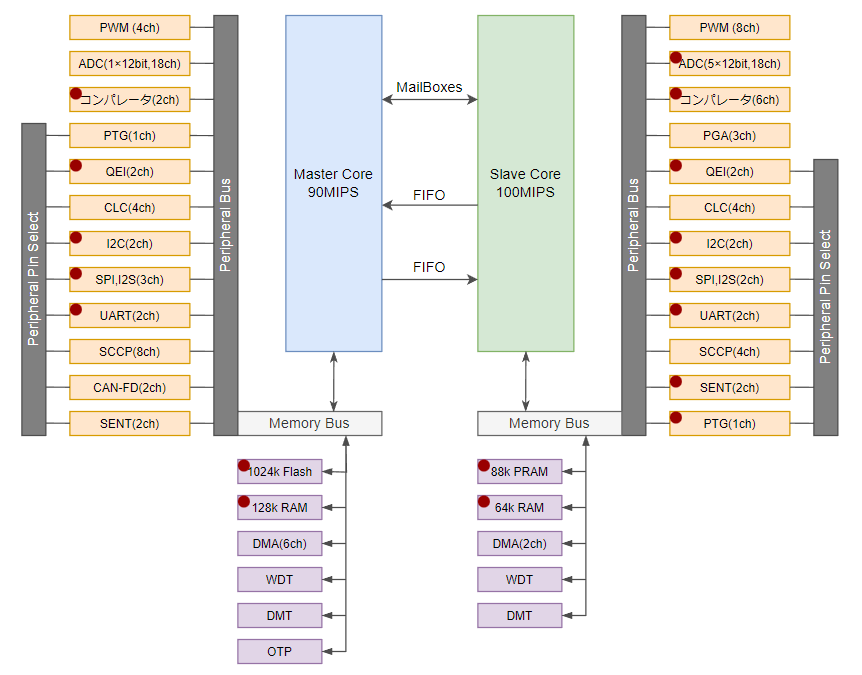

(23/10/14追記)dsPIC33CH1024MP7xxシリーズの構成(予想)

23/10/14の時点で正式にはまだ発表されていない模様ですが、MPLABX上で確認できる最新のdsPIC33CH1024MP7xxシリーズの構成は以下の通りと予想されます。

赤丸が従来からの更新点で、全体的なメモリの強化やスレーブ側のコアが特に強化されている事が判ります。

■第1世代

| Flash =64kB | Flash =128kB | ADC | DAC/CMP | CAN-FD | QEI | CLC | UART | I2C | SPI | Internal BackConv. | |

| 200系 | dsPIC33CH64MP202(S1) dsPIC33CH64MP203(S1) dsPIC33CH64MP205(S1) dsPIC33CH64MP206(S1) dsPIC33CH64MP208(S1) | dsPIC33CH128MP202(S1) dsPIC33CH128MP203(S1) dsPIC33CH128MP205(S1) dsPIC33CH128MP206(S1) dsPIC33CH128MP208(S1) | (M)×1 (S)×3 | (M)×1 (S)×3 | 0 | (M)×1 (S)×1 | (M)×4 (S)×4 | (M)×2 (S)×1 | (M)×2 (S)×1 | (M)×2 (S)×1 | No |

| 500系 | dsPIC33CH64MP502(S1) dsPIC33CH64MP503(S1) dsPIC33CH64MP505(S1) dsPIC33CH64MP506(S1) dsPIC33CH64MP508(S1) | dsPIC33CH128MP502(S1) dsPIC33CH128MP503(S1) dsPIC33CH128MP505(S1) dsPIC33CH128MP506(S1) dsPIC33CHMP508(S1) | (M)×1 (S)×3 | (M)×1 (S)×3 | (M)×1 | (M)×1 (S)×1 | (M)×4 (S)×4 | (M)×2 (S)×1 | (M)×2 (S)×1 | (M)×2 (S)×1 | No |

■第2世代

| Flash =256kB | Flash =512kB | ADC | DAC/CMP | CAN | QEI | CLC | UART | I2C | SPI | Internal BackConv. | |

| 200系 | dsPIC33CH256MP205(S1) dsPIC33CH256MP206(S1) dsPIC33CH256MP208(S1) | dsPIC33CH512MP205(S1) dsPIC33CH512MP206(S1) dsPIC33CH512MP208(S1) | (M)×1 (S)×3 | (M)×1 (S)×3 | 0 | (M)×1 (S)×1 | (M)×4 (S)×4 | (M)×2 (S)×1 | (M)×2 (S)×1 | (M)×2 (S)×1 | No |

| 500系 | dsPIC33CH256MP505(S1) dsPIC33CH256MP506(S1) dsPIC33CH256MP508(S1) | dsPIC33CH512MP505(S1) dsPIC33CH512MP506(S1) dsPIC33CH512MP508(S1) | (M)×1 (S)×3 | (M)×1 (S)×3 | (M)×2 | (M)×1 (S)×1 | (M)×4 (S)×4 | (M)×2 (S)×1 | (M)×2 (S)×1 | (M)×2 (S)×1 | No |

■第3世代

| Flash =512kB | Flash =1024kB | ADC | DAC/CMP | CAN | QEI | CLC | UART | I2C | SPI | Internal BackConv. | |

| 300系 | dsPIC33CH512MP305(S1) dsPIC33CH512MP306(S1) dsPIC33CH512MP308(S1) | dsPIC33CH1024MP305(S1) dsPIC33CH1024MP306(S1) dsPIC33CH1024MP308(S1) | (M)×1 (S)×5 | (M)×2 (S)×6 | 0 | (M)×2 (S)×2 | (M)×4 (S)×4 | (M)×2 (S)×2 | (M)×2 (S)×1 | (M)×3 (S)×2 | No |

| 400系 | dsPIC33CH512MP405(S1) dsPIC33CH512MP406(S1) dsPIC33CH512MP408(S1) dsPIC33CH512MP410(S1) dsPIC33CH512MP412(S1) | dsPIC33CH1024MP405(S1) dsPIC33CH1024MP406(S1) dsPIC33CH1024MP408(S1) dsPIC33CH1024MP410(S1) dsPIC33CH1024MP412(S1) | (M)×1 (S)×5 | (M)×2 (S)×6 | 0 | (M)×2 (S)×2 | (M)×4 (S)×4 | (M)×2 (S)×2 | (M)×2 (S)×1 | (M)×3 (S)×2 | Yes |

| 600系 | dsPIC33CH512MP605(S1) dsPIC33CH512MP606(S1) dsPIC33CH512MP608(S1) | dsPIC33CH1024MP605(S1) dsPIC33CH1024MP606(S1) dsPIC33CH1024MP608(S1) | (M)×1 (S)×5 | (M)×2 (S)×6 | (M) × 2 | (M)×2 (S)×2 | (M)×4 (S)×4 | (M)×2 (S)×2 | (M)×2 (S)×1 | (M)×3 (S)×2 | No |

| 700系 | dsPIC33CH512MP705(S1) dsPIC33CH512MP706(S1) dsPIC33CH512MP708(S1) dsPIC33CH512MP710(S1) dsPIC33CH512MP712(S1) | dsPIC33CH1024MP705(S1) dsPIC33CH1024MP706(S1) dsPIC33CH1024MP708(S1) dsPIC33CH1024MP710(S1) dsPIC33CH1024MP712(S1) | (M)×1 (S)×5 | (M)×2 (S)×6 | (M) × 2 | (M)×2 (S)×2 | (M)×4 (S)×4 | (M)×2 (S)×2 | (M)×2 (S)×1 | (M)×3 (S)×2 | Yes |

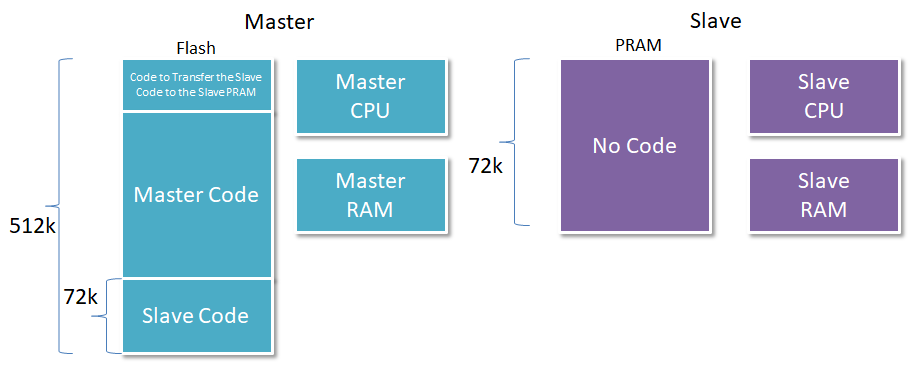

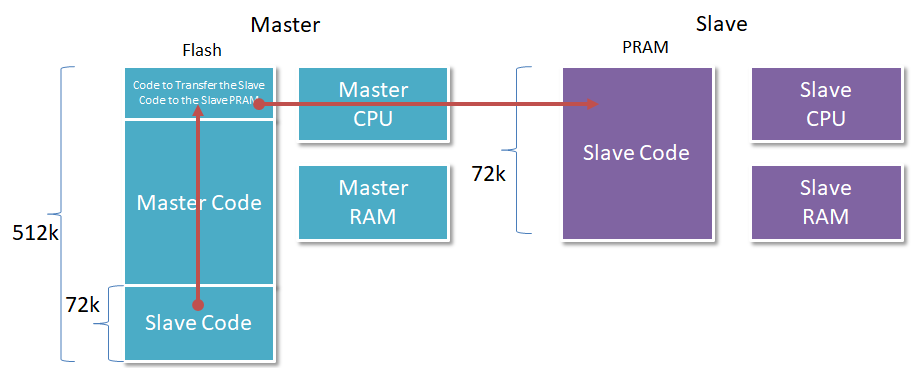

スレーブメモリ構成

特徴としてスレーブコアにはフラッシュメモリが搭載されておらず、Program RAM Memory(PRAM)という揮発性のプログラム領域を有しております。起動時にはこのPRAM領域に何もプログラムが書かれておらず、実行できません。

スレーブ側のプログラムはマスター側のフラッシュメモリ領域の内、最大72kB内に書き込まれ、マスター側のプログラムでスレーブ側のPRAM領域に転送を指示する事でスレーブ側が動作する構造となっております。

まとめ dsPIC33CHファミリの利点

- デュアル独立コアによるファームウェア開発の簡素化

- デュアルコアと周辺機器セットにより、堅牢なシステムが促進され、機能安全の向上

- 2ch CAN-FD(33CH256/512)によりCAN通信の帯域幅増加

- 高速ADC、波形生成機能付きDAC、アナログコンパレータ、PGA等のアナログ統合

- 高可用性システムのファームウェアのライブ更新

といった利点があげられます。

コメント