概要

かつては74HCシリーズなどを組み合わせて論理回路を構成していました。そのため回路規模が大きく、修正も容易ではないなど時代に合わなくなってきました。

その後PLD(Programmable Logic Array)と呼ばれる内部の論理回路を再構成できる半導体チップが登場しました。回路規模の大きさや中の構成で方法などで「CPLD」や「FPGA」と呼ばれるチップが現在でも使われています。

その様な内部の論理回路を構成可能な CLCモジュールがMicrochip社の最近の8bit、16bitマイコンにはほぼ搭載されており、dsPIC33CHシリーズではCLCモジュールがマスターに4ch、スレーブに4ch搭載されています。

Configurable Logic Cellの略でANDやOR、フリップフロップなどのロジック機能を組み合わせて論理回路を構成可能なモジュール。

CPLDやFPGAのようにVHDLやVerilog等で記述する訳でなく、レジスタの設定で構成する。複雑なロジック回路は構成できないが、動的に論理回路を変更可能

- ソフトウェアに比べハードウェアなので高速に信号処理が可能

- 外付け部品は不要で、集積度を高めて基板面積とシステムコストを削減可能

- 他のモジュールと組み合わせる事で、機能の拡張が可能

- CPUに負荷をかけない

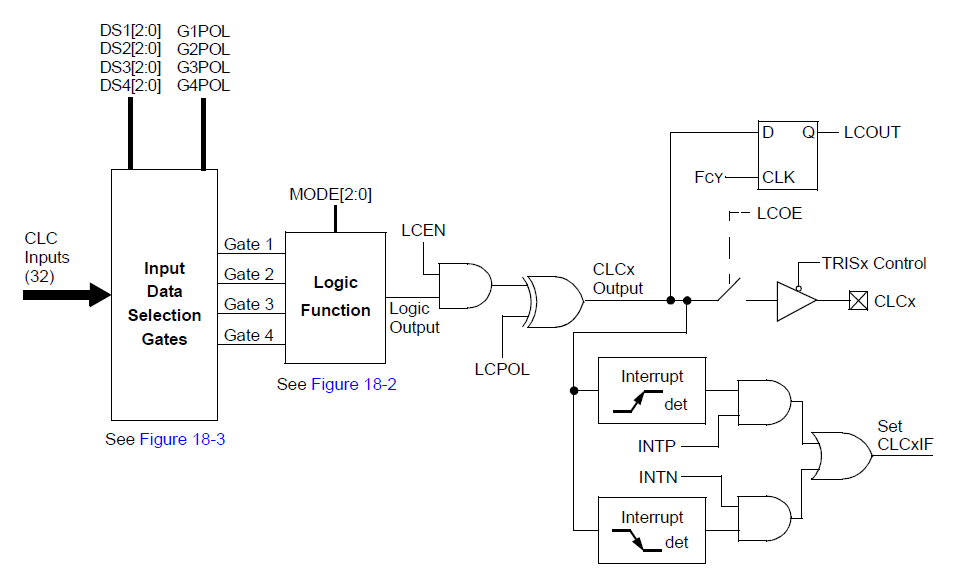

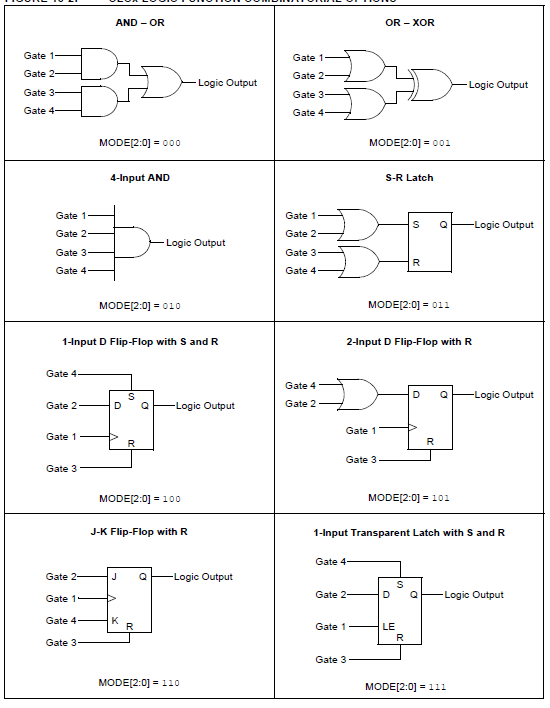

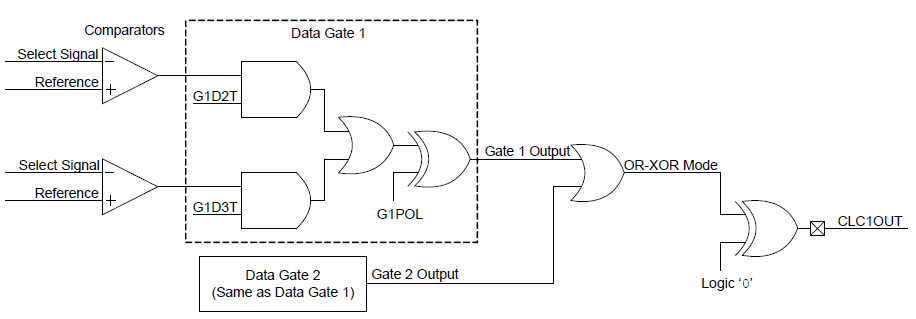

CLCの全体ブロックは(fig.2)の様になっており、入力選択ゲートブロック (fig.3)、 ロジック機能選択(fig.4)、出力制御部に分かれています。

入力選択ゲートブロックは以下の様な機能を持ちます。

- データセレクション(1~4)毎に8つの入力から1つを選択

- データゲート(1~4)は各データセレクション出力(非反転・反転)を有効化し、論理和をとった信号をゲート部へ出力します。

PIC18系ですとデータセレクションは127の入力から1つを選択可能となっていますので、ルーティングに制限が有ります。

ロジック機能選択ブロックは主に「ゲート」部と「ラッチ」部で構成されます。つまり「カウンタ」などは実質構成できず他のペリフェラル(CCPやNCOなど)と組み合わせ実現させます。

レジスタ

CLC関連のレジスタは以下の5種類

| レジスタ名 (x = 1~6) | 機能 | 説明 |

| CLCxCONL CLCxCONH | DMA High Address Limit Registers | はモジュール、割り込み、ピン出力の有効 / 無効の設定と、 ロジック機能の選択を行う |

| CLCxSEL | DMA ENGINE CONTROL REGISTER | 4つのデータ選択マルチプレクサ のそれぞれで、8 つの入力信号から 1 つを選択します |

| CLCxGLSL CLCxGLSH | DMA CHANNEL n CONTROL REGISTER | CLCxSEL レジスタで選択されている 4 つの入力信号源から 4 つの論理演算値 ( ゲート出力 ) を生成 |

ロジック構成例

CLC単体や他のモジュールと組み合わせて様々なハードウェア機能を構成可能です。

以下マイクロチップ社のデータシートに掲載されているアプリケーションの例を紹介します。

• 論理式

• 順次ロジック回路

• エンコーダ/デコーダ

• カウンタ

• マルチプレクサ

• 割り込みを使わないリアルタイム データキャプチャ

• 複雑な波形生成(例: IR 送信用のNEC コード)

• サイクロコンバータ

• 位相検出回路

• 周波数分周回路

• パルス幅伸長回路

• PWM ステアリング

• 信号しきい値およびサンプルホールド制御回路

• スイッチのデバウンス

高速パルス検出/拡張

フリップフロップのD入力を常に「Hi」とし、高速パルスの立ち上がりでラッチします。CPU側でCLC出力を処理した後に、ソフトウェアでリセット入力(Gate3)の信号を(Hi)に設定(CLCxCONHbits.G3POL =1)にするとラッチが解除可能

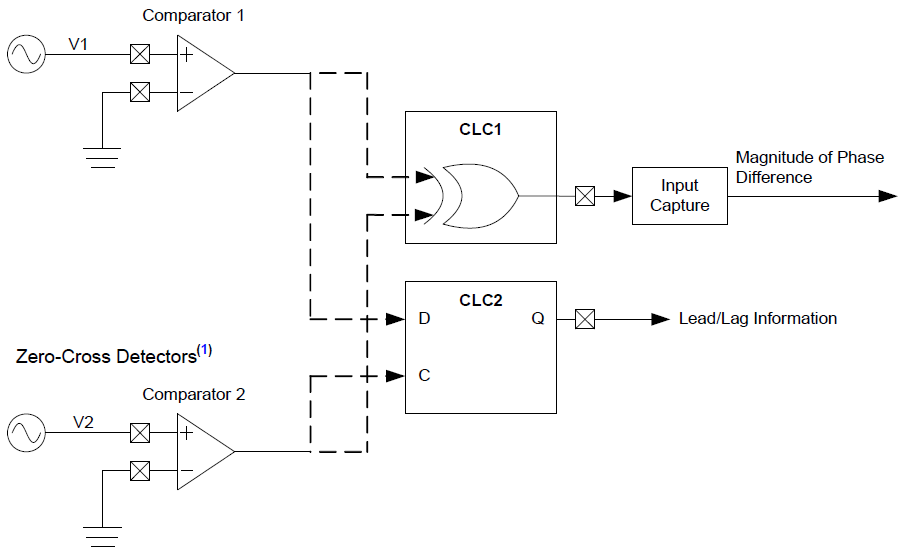

位相検出器

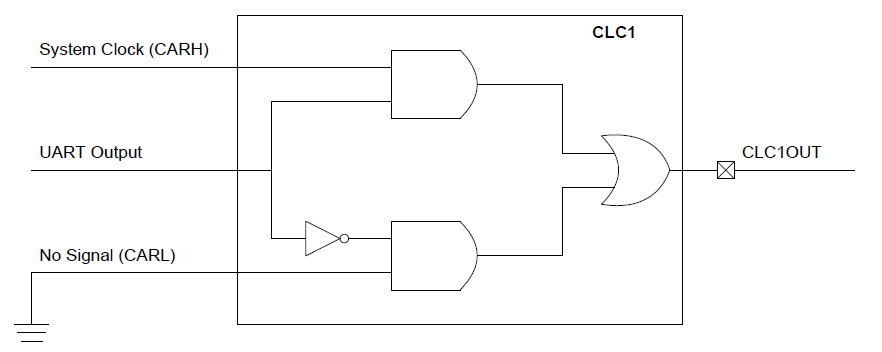

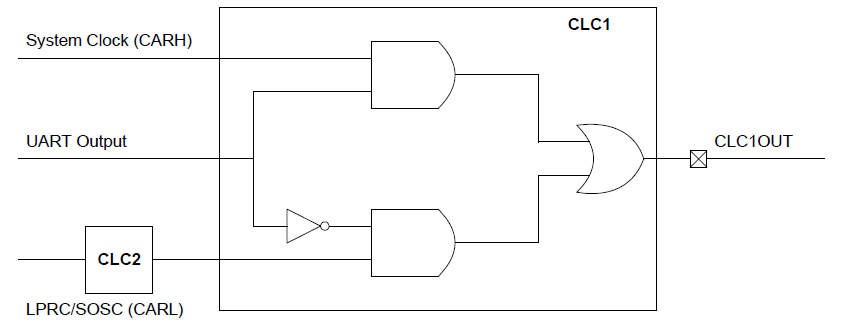

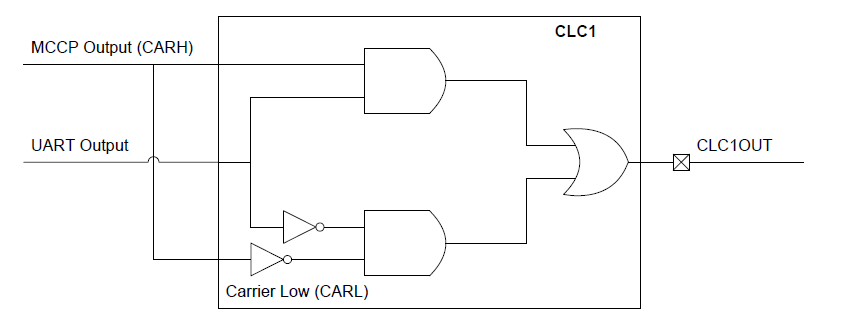

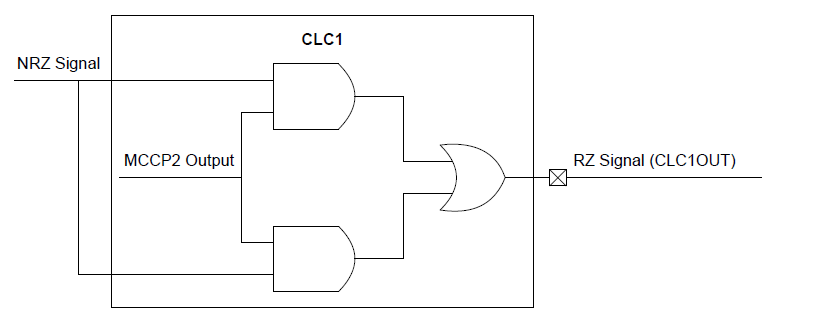

デジタル変調

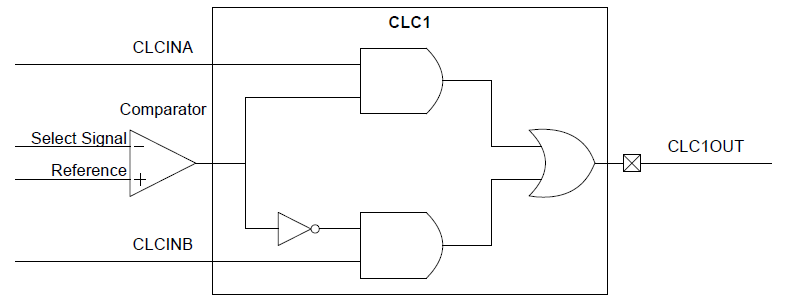

複数パラメータの監視

通信信号エンコーダ

マルチプレクサ

ソースコード

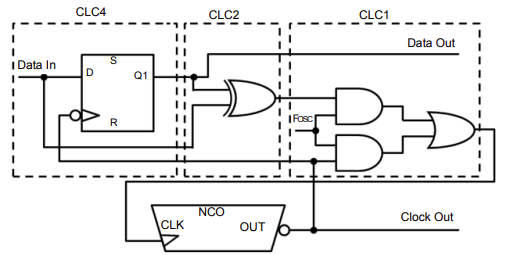

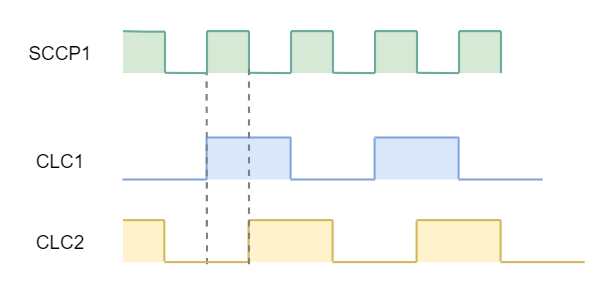

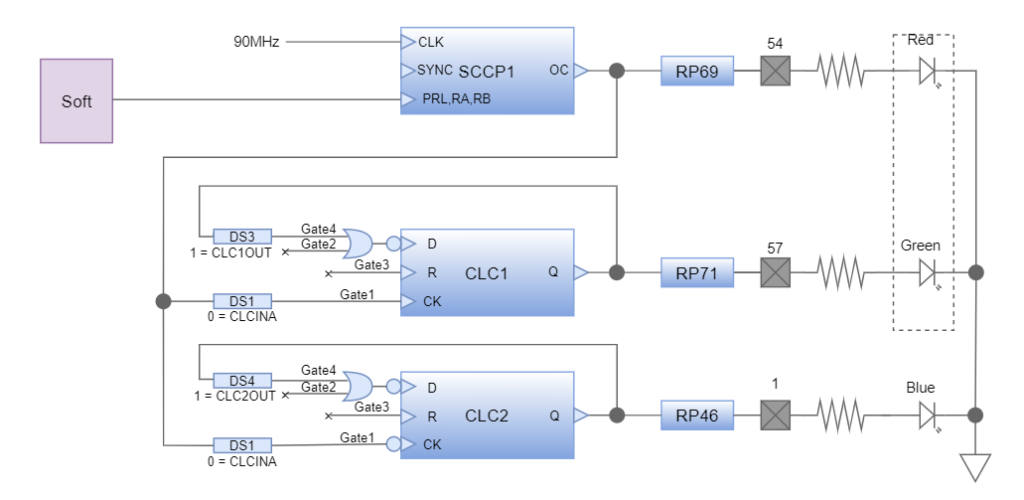

例としてクロック逓倍&90度位相シフト回路。クロックはダミー信号としてSCCP1からの信号を用います。

コンフィグレーション設定についてはコンフィグレーション設定に記載しております。

コピーして下記のソースコードの「 //ここにコンフィグレーション設定を挿入する// 」の位置に挿入してください。

クロック設定用関数 vds_Main_Init_Clock_Register(); のソースコードはクロック設定のページに記載しております。

コピーして下記のソースコードの「 //ここにクロック設定ソースをコピペする// 」の位置に挿入してください。

/*------------------------------------------------------------------------------*/

/* @file CLC.c */

/* @brief CLCサンプル */

/* @details */

/*------------------------------------------------------------------------------*/

/*------------------------------------------------------------------------------*/

/* コンフィグレーション設定*/

/*------------------------------------------------------------------------------*/

//ここにコンフィグレーション設定を挿入する//

/*------------------------------------------------------------------------------*/

/* インクルードファイル*/

/*------------------------------------------------------------------------------*/

#include <stdio.h>

#include <stdlib.h>

#include <xc.h>

/*------------------------------------------------------------------------------*/

/* 定数定義*/

/*------------------------------------------------------------------------------*/

/*------------------------------------------------------------------------------*/

/*【V変数定義*/

/*------------------------------------------------------------------------------*/

/*------------------------------------------------------------------------------*/

/* クロック設定 */

/*------------------------------------------------------------------------------*/

//ここにクロック設定ソースを挿入する//

/*------------------------------------------------------------------------------*/

/* Main関数 */

/*------------------------------------------------------------------------------*/

int main(int argc, char** argv)

{

/*--------------------------------------------------------------------------*/

/* クロック初期化*/

/*--------------------------------------------------------------------------*/

vds_Main_Init_Clock_Register(); /* クロック初期化 */

/*--------------------------------------------------------------------------*/

/* リマッパブルピン初期化*/

/*--------------------------------------------------------------------------*/

RPOR18bits.RP69R = 15u; /* RGB LED RED [SCCP1] */

RPINR45bits.CLCINAR = 69;

RPOR19bits.RP71R = 40; /* CLC1out */

RPOR7bits.RP46R = 41; /* CLC2out */

/*-------------------------------------------------------------------------*/

/* CCP1初期化*/

/*-------------------------------------------------------------------------*/

CCP1CON1L = 0x0000u;

CCP1CON1Lbits.MOD = 4u; /* PWMモード*/

CCP1CON1Lbits.CCSEL = 0u; /* コンペアモード */

CCP1CON1H = 0x0000u;

CCP1CON1Hbits.SYNC = 0u; /* 同期無し */

CCP1CON2H = 0x0000u;

CCP1CON2Hbits.OCAEN = 1u; /* 出力イネーブル */

CCP1CON3H = 0x0000u;

CCP1CON3Hbits.POLACE = 1u; /* CCPx 出力ピン 極性制御ビット */

CCP1PRL = 3000;

CCP1RB = 1500u;

/*-------------------------------------------------------------------------*/

/* CLC1*/

/*-------------------------------------------------------------------------*/

CLC1SEL = 0x0100u;

CLC1SELbits.DS1 = 0u; /* CLCINA */

CLC1SELbits.DS3 = 1u; /* Master CLC1 output */

CLC1CONH = 0x0008u;

CLC1CONHbits.G4POL = 1u;

CLC1GLSL = 0x0002u;

CLC1GLSLbits.G1D1T = 1u;

CLC1GLSH = 0x2000u;

CLC2GLSHbits.G4D3T = 1u;

CLC1CONL = 0x8085u;

CLC1CONLbits.MODE = 5u; /* Two-input D flip-flop with R*/

CLC1CONLbits.LCOE = 1u; /* 出力有効化 */

CLC1CONLbits.LCEN = 1u; /* モジュール有効化 */

/*-------------------------------------------------------------------------*/

/* CLC2*/

/*-------------------------------------------------------------------------*/

CLC2SEL = 0x1000u;

CLC1SELbits.DS1 = 0u; /* CLCINA */

CLC2SELbits.DS4 = 1u; /* Master CLC2 output */

CLC2CONH = 0x0009u;

CLC2CONHbits.G1POL = 1u;

CLC2CONHbits.G4POL = 1u;

CLC2GLSL = 0x0002u;

CLC2GLSLbits.G1D1T = 1u;

CLC2GLSH = 0x8000u;

CLC2GLSHbits.G4D4T = 1u;

CLC2CONL = 0x8085u;

CLC2CONLbits.MODE = 5u; /* Two-input D flip-flop with R*/

CLC2CONLbits.LCOE = 1u; /* 出力有効化 */

CLC2CONLbits.LCEN = 1u; /* モジュール有効化 */

/*-------------------------------------------------------------------------*/

/* CCPの有効化*/

/*-------------------------------------------------------------------------*/

CCP1CON1Lbits.CCPON = 1u ;

while(1)

{

}

}

コメント