はじめに

1.概要

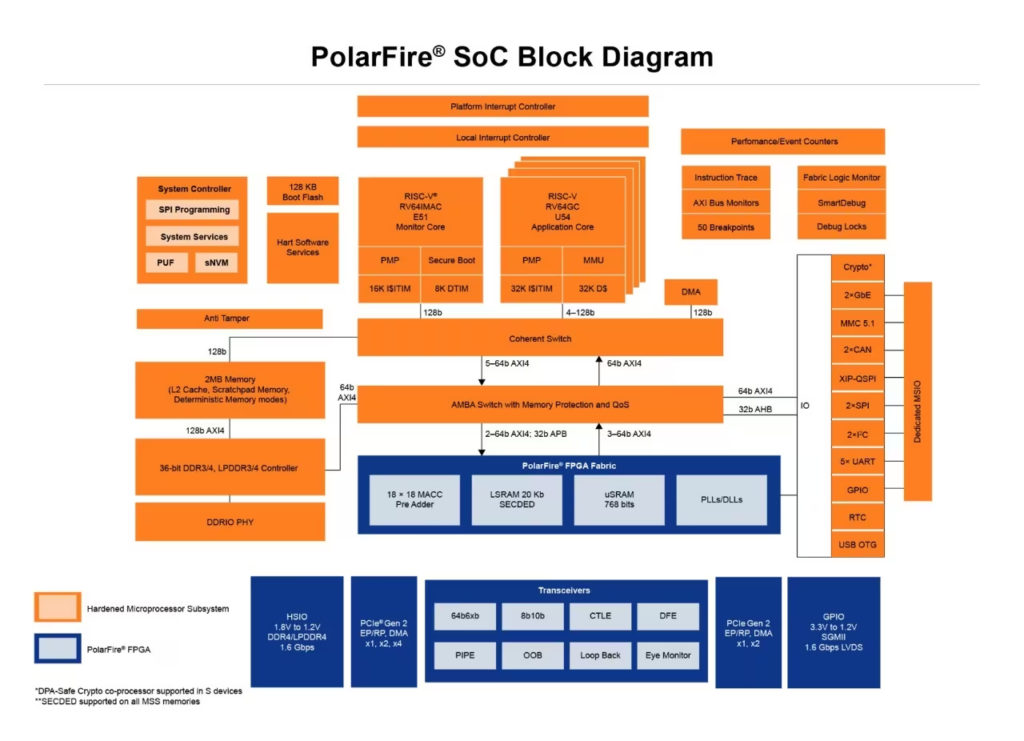

Microchip社のPolarFire® SoCは、不揮発性で低消費電力のミッドレンジSoC FPGAで、64ビットのRISC-V ISAを5コア搭載したプロセッサーと低消費電力FPGAを組み合わせたチップです。

・PolarFire® SoC FPGAs | Microchip Technology

・Microchip Technology社 不揮発性SoC FPGA「PolarFire SoC」 – Microchip – マクニカ (macnica.co.jp)

intel(旧Altera)やAMD(旧ザイリンクス)のようなハイエンド向けではありませんが、高度なセキュリティ機能を有していますので、電力効率が高くセキュアなアプリケーション向けに使用されます。

2.この記事の目的

この記事は私の忘備録も兼ねて、PolarFire®SoCのFPGAにてLチカが出来る事を目指しています。

3.構成

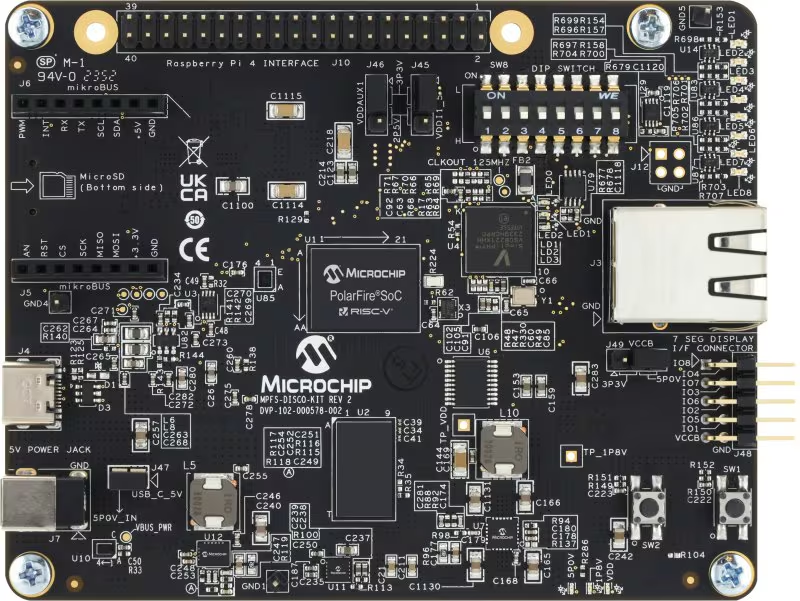

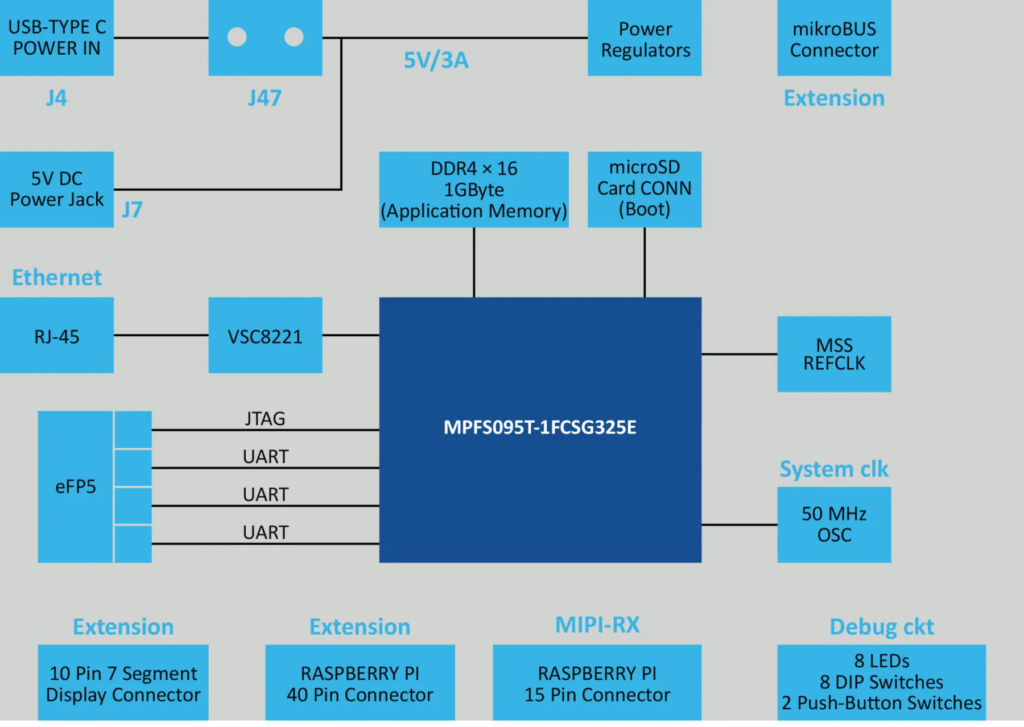

PolarFire® SoC Discovery Kitを使用し、動作を確認していきます。

PolarFire® SoC Discovery Kit | Microchip Technology

Microchip Directでおおよそ23,000円程度で購入できます。Digikeyでチップ単体を購入すると約38,000円程度かかるので、この開発キットはかなり安いと感じます。

Lチカまでの道のり①

Lチカの前にまずは PolarFire® SoC Discovery Kit Quickstart Card (microchip.com) を参考に、デフォルトでインストールされているフィルターソフトを実行します。

1.ソフトのセットアップ

①Libero® SoC 2024.1 のダウンロードとインストールを行います。Libero SoCは、アプリケーションの開発に使用される設計ツールです。

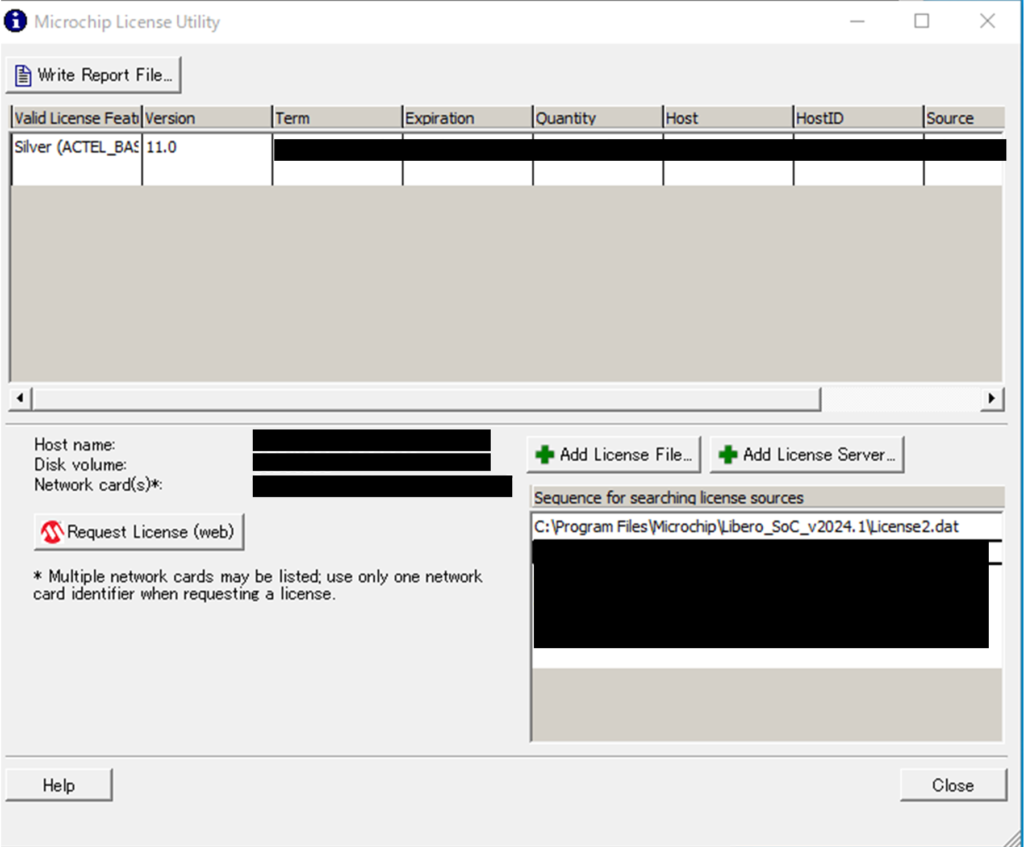

②Libero SoC Design Suite のシルバーライセンスを取得します。 MicrochipDirectからLibero Silverライセンスを生成します。

①シルバーライセンスには「Libero Silver 1 Yr DiskID NL License」と「Libero Silver 1Yr Floating License for Windows/Linux Server」が有りますが「Libero Silver 1 Yr DiskID NL License」を選択します。

②登録にはCドライブのDISK IDを求められますが、以下の2つの方法で確認ができます。

1)Microsemi(Microchip) License Utilityを立ち上げ、Disk volume の行に記載されている8桁16進数の値

2)コマンドプロンプトを立ち上げ 「C:\>Vol C:」とタイプする。

③DISK IDを入力し、問題なければ数分でMicrochipからライセンスファイルが添付されたメールが届きます。

④Microsemi(Microchip) License Utilityの「Add License File」ボタンをクリックし、ローカルに保存されたライセンスファイルを指定します。

⑤正常であればデータグリッドビューにライセンスが表示されます。

③PolarFire® SoC MSS Configurator | Microchip Technology のダウンロードとインストールを行います。PolarFire® SoCマイクロプロセッササブシステム(MSS)コンフィギュレータは、PolarFire SoCマイクロプロセッササブシステムを構成するためのソフトウェアツールです。Libero SoC Design Suite v12.5以降のインストール時に同時にMSSコンフィギュレータがインストールされます。※今回の記事では使用しません。

④ソフトコンソール |マイクロチップ・テクノロジー (microchip.com)のダウンロードとインストールを行います。SoftConsoleは、ベアメタルおよびRTOSベースのC/C++ソフトウェアを迅速に開発するためのソフトウェア開発環境です。※今回の記事では使用しません。

⑤AN5165 | Application Note | Microchip Technology デモソフトのダウンロードとインストールを行います。

2.ハードウェアのセットアップ

①基板のジャンパーピンを以下の設定にします。私の購入時にはデフォルトで下記の状態になっていました。

| JP | 状態 | 役割 |

| JP46 | 1-2ショート | VDDAUX1電圧の設定 (1-2ショート = 3.3V / 2-3ショート = 2.5V) |

| JP45 | 1-2ショート | VDDI1_5電圧の設定 (1-2ショート = 3.3V / 2-3ショート = 2.5V) |

| JP49 | 2-3ショート | VCCB電圧の設定 (1-2ショート = 3.3V / 2-3ショート = 5V) |

| JP47 | 1-2ショート | 外部入力電圧の設定 (1-2ショート = USB-5Vを使用 / 1-2オープン = 外部5Vを使用) |

②FTDIのDrivers – FTDI (ftdichip.com) ドライバーをインストールします。有名どころですのでインストール不要の場合もあるかもしれません。

ドライバをインストールしたら、基板とPCをUSB Type-Cを接続します。正常にインストールされていれば、下記の通り3つのCOMポートが表示されます。

3.デモソフトの実行

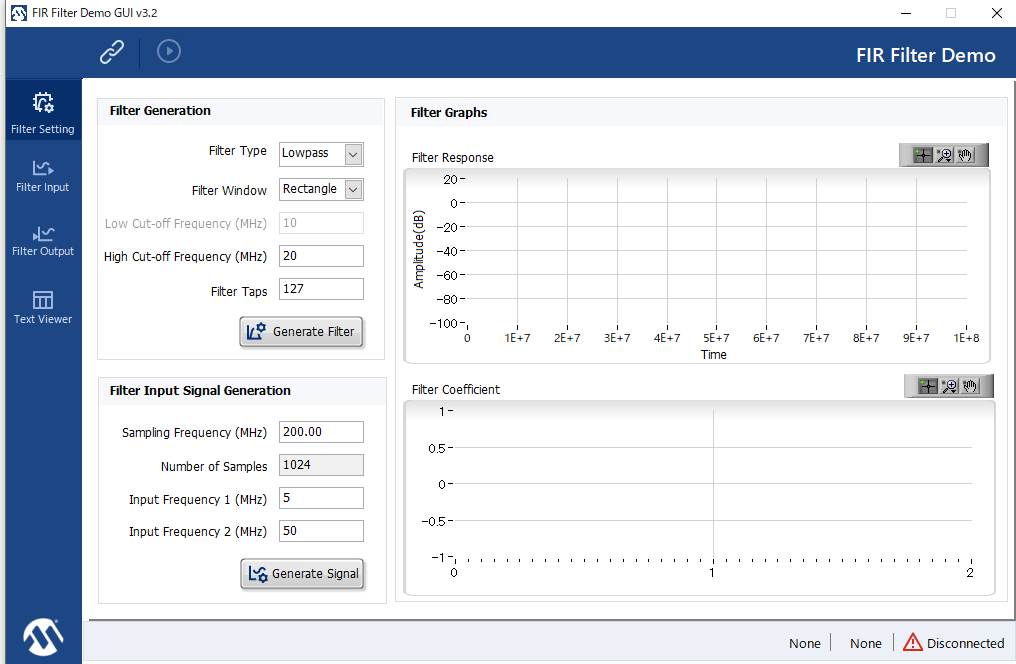

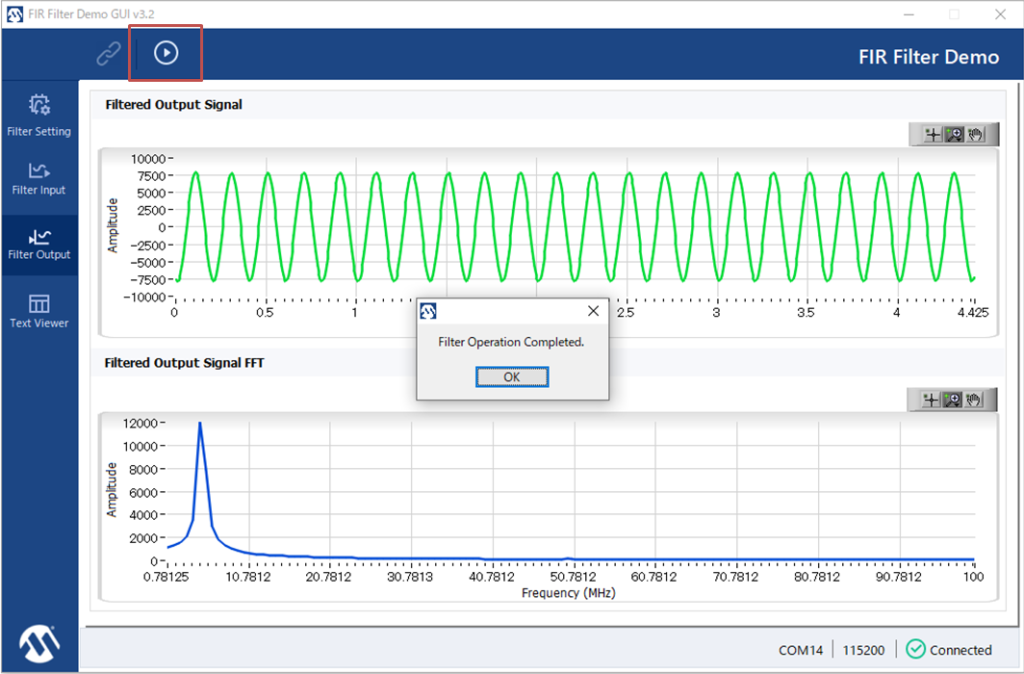

①PC上でGUIソフトを起動します。

②上記の鎖アイコンをクリックすると、ボードの接続待ちに遷移します。ボード上のSW1を押しダイアログのOKを押すと接続が完了します。

③Generate Filterをクリックすると、127タップ/カットオフ20MHzのフィルターが生成されます。

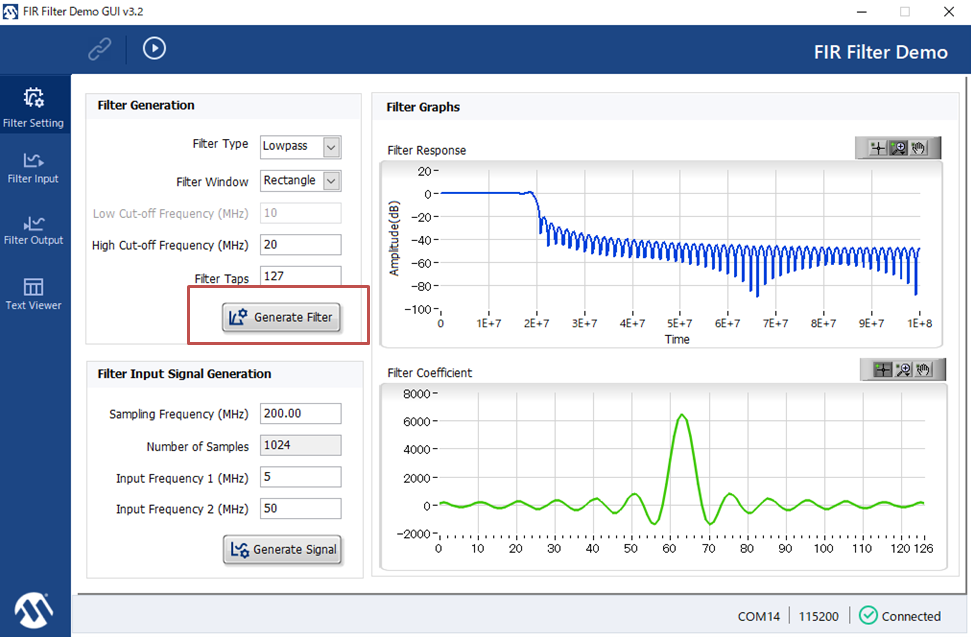

④次にGenerate Signalをクリックしダミー信号を生成します。

⑤左のペインのFilter Inputをクリックすると入力信号とスペクトルが表示されます

⑥再生ボタンを押すとPolarFire® SoCと通信が行われ、結果が表示されます。50MHzの成分は除去されている事が判ります。

Lチカまでの道のり②

次はAN5282: PolarFire SoC Design Flow Application Note (microchip.com) を参考に基板上の2つのSWをどちらか押した時にLEDが消灯するプロジェクトを生成します。

1.プロジェクトの新規作成

①Libero SOC Design Suite アプリを起動し、左のペインからNewをクリックします。

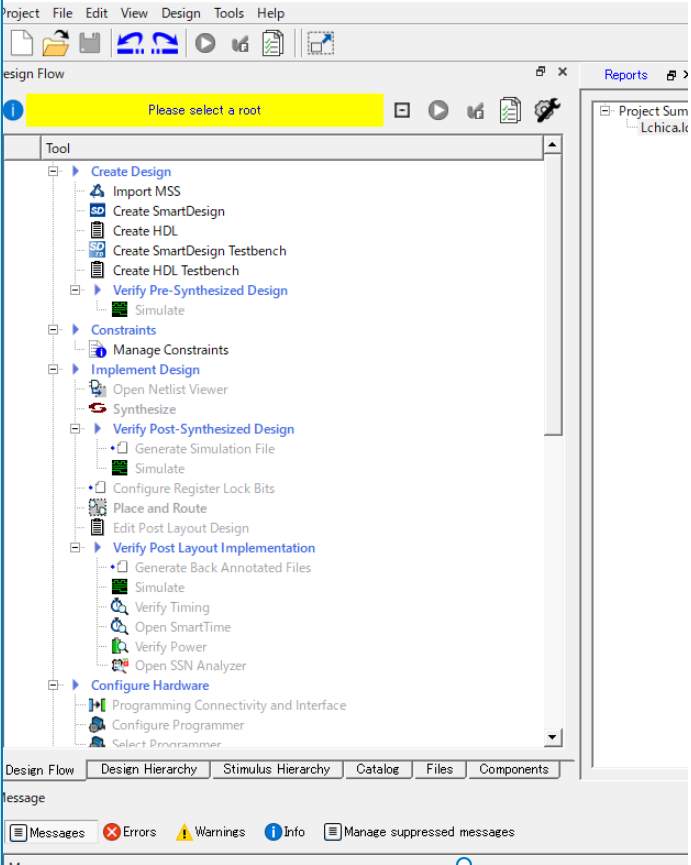

(fig.2-1-1)Libero SOC Design Suite起動画面

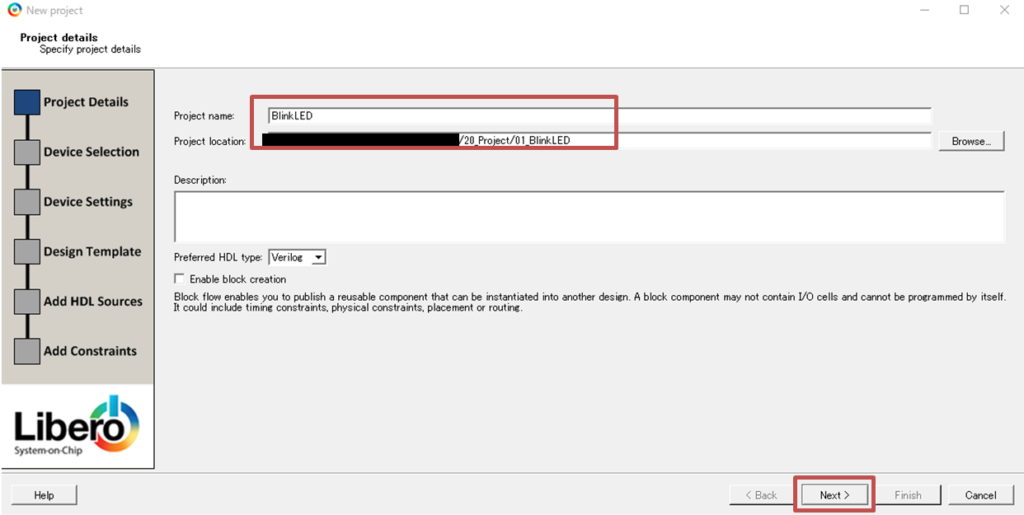

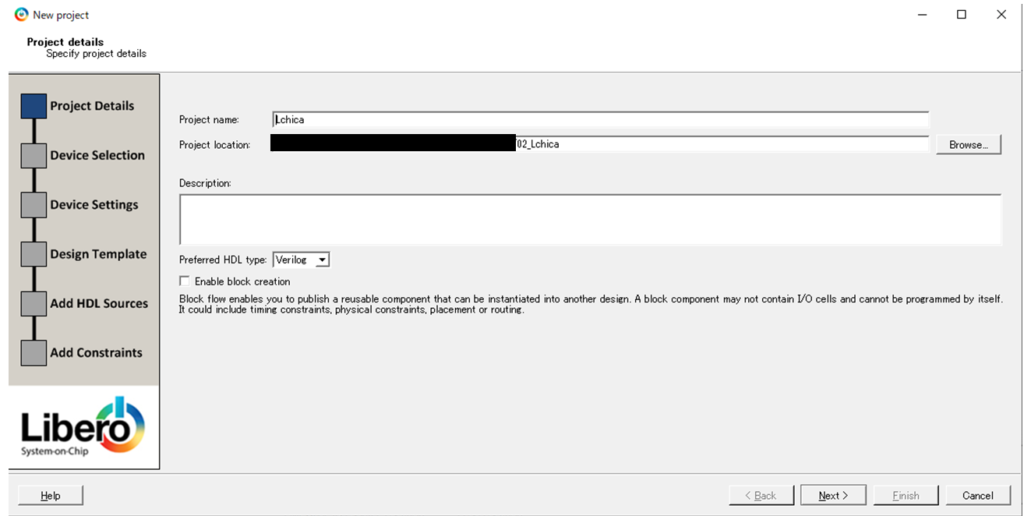

②プロジェクトの名前と保存場所を入力しNextをクリックします。VHDLかVerilogかは自由ですが個人的にVerilogを触ったことが無かったのでVerilogにします。

(fig.2-1-2)Libero SOC Design Suite新規プロジェクト作成

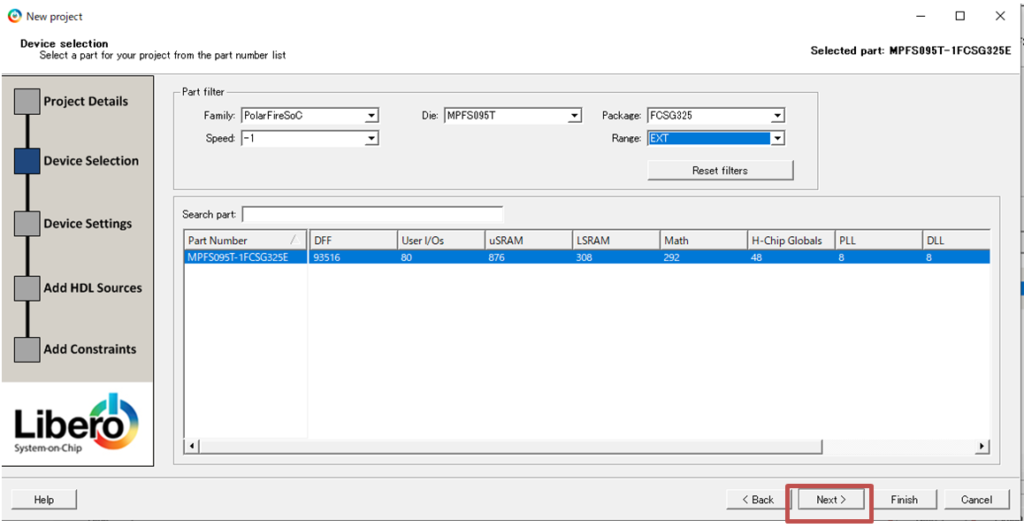

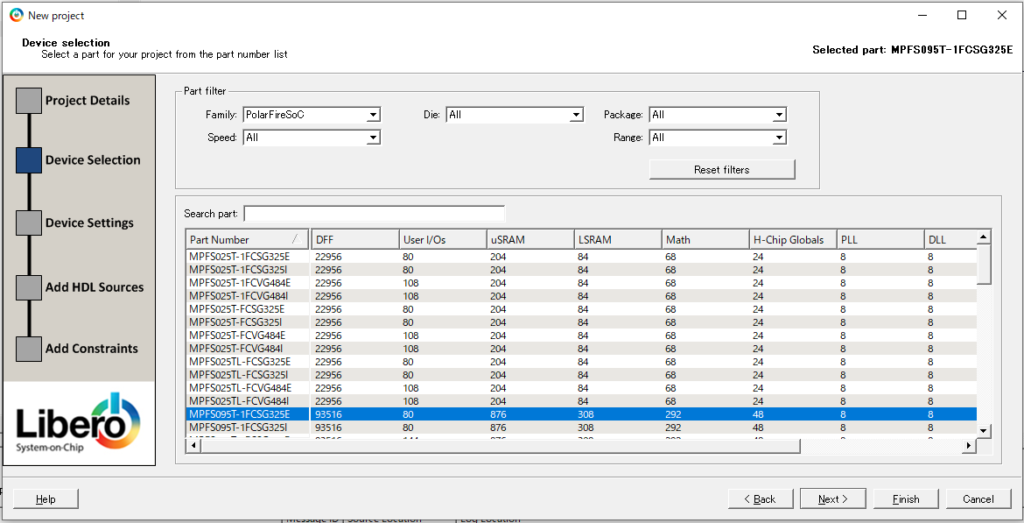

③Device Selection画面では以下のように設定します。

| 項目 | 値 |

| Family | PolarFilre SoC |

| Die | MPFS095T |

| Package | FCSG325 |

| Speed | -1 |

| Range | EXT |

| Part Number | MPFS095T-1FCSG325E |

(fig.2-1-3)Device Selection設定

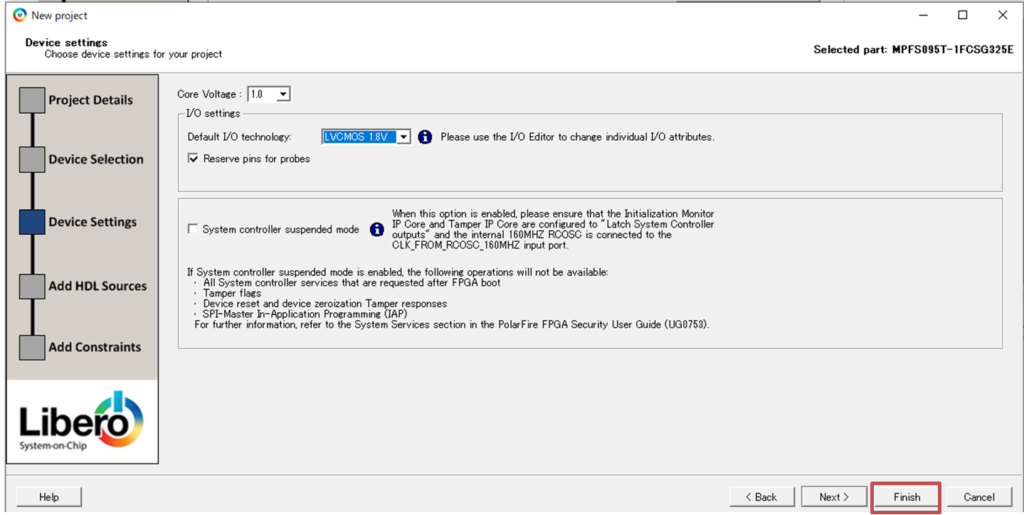

④Device Setting画面では以下のように設定し、「Finish」を選択します。

| 項目 | 値 |

| Core Voltage | 1.0 |

| Default I/O technology | LVCMOS 1.8V |

| Reserve pin for probes | チェック オン |

| System controller suspended mode | チェック オフ |

2.デザインの作成

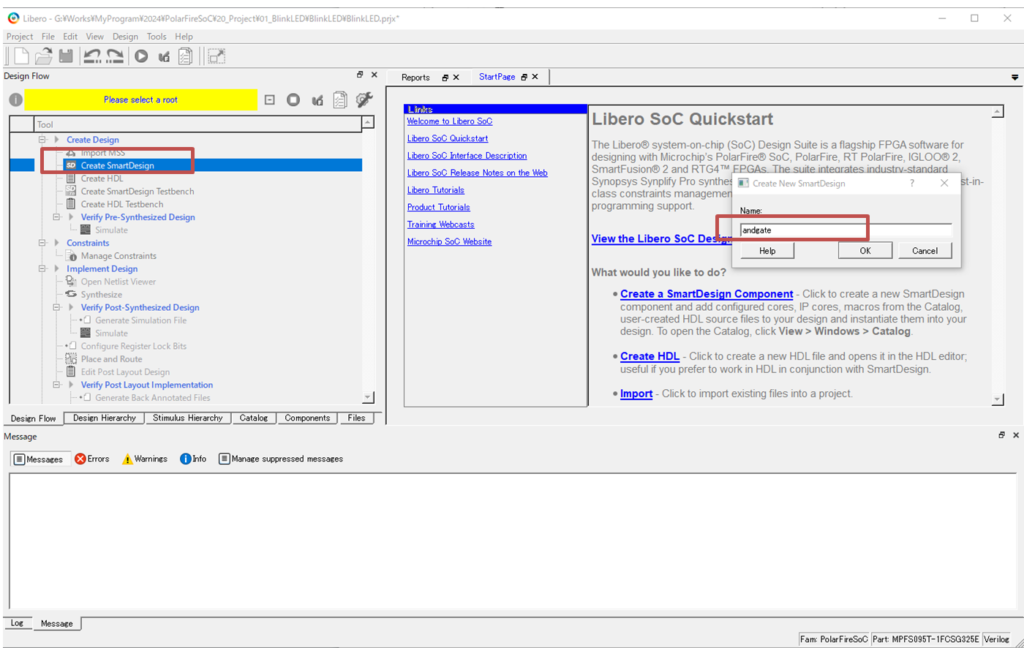

①Create SmartDesignをダブルクリックし、Create New SmartDesignダイアログのNameに「andgate」と入力しOKをクリックします。

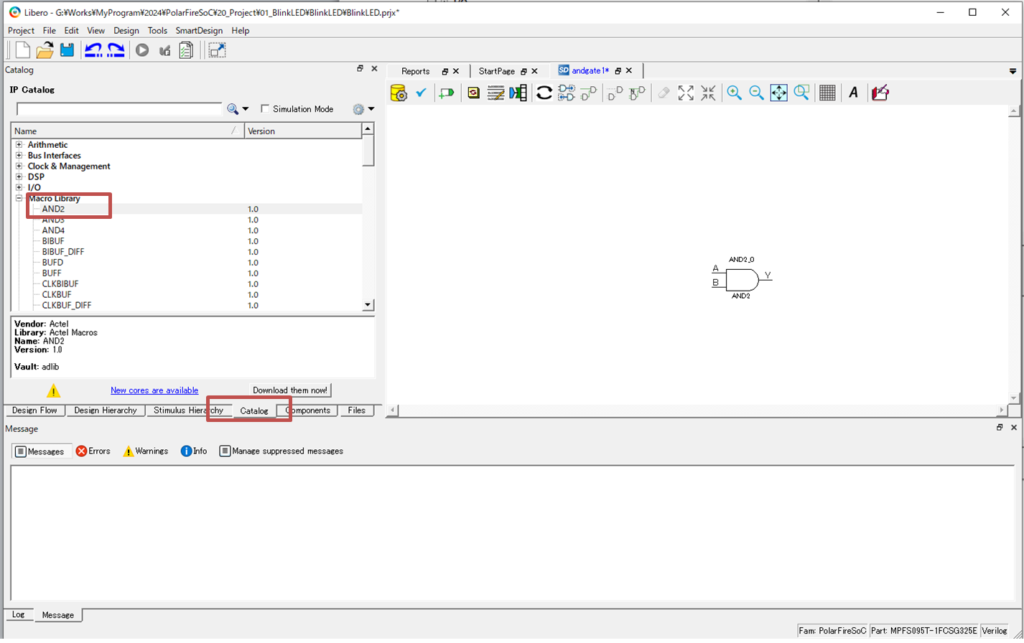

②CatalogタブからMacro Library展開し「AND2」をダブルクリックします。

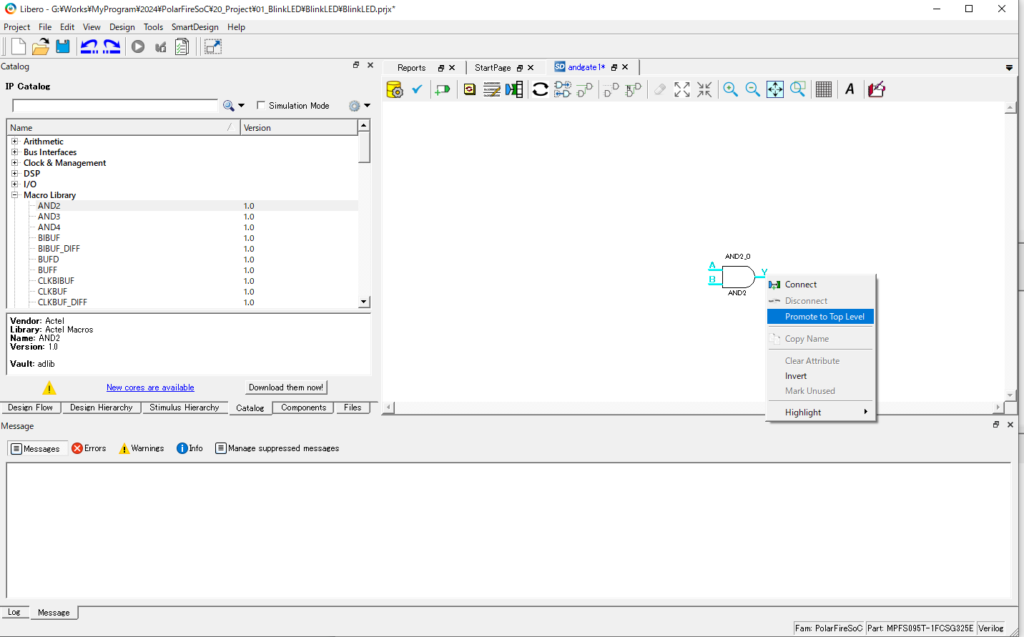

③ANDゲートのA,B,Yピンを選択し、右クリックでメニューを開き、「Prompto Top Level」をクリックします。

④これにより外部接続可能なピンが生成されますので、一旦保存します。

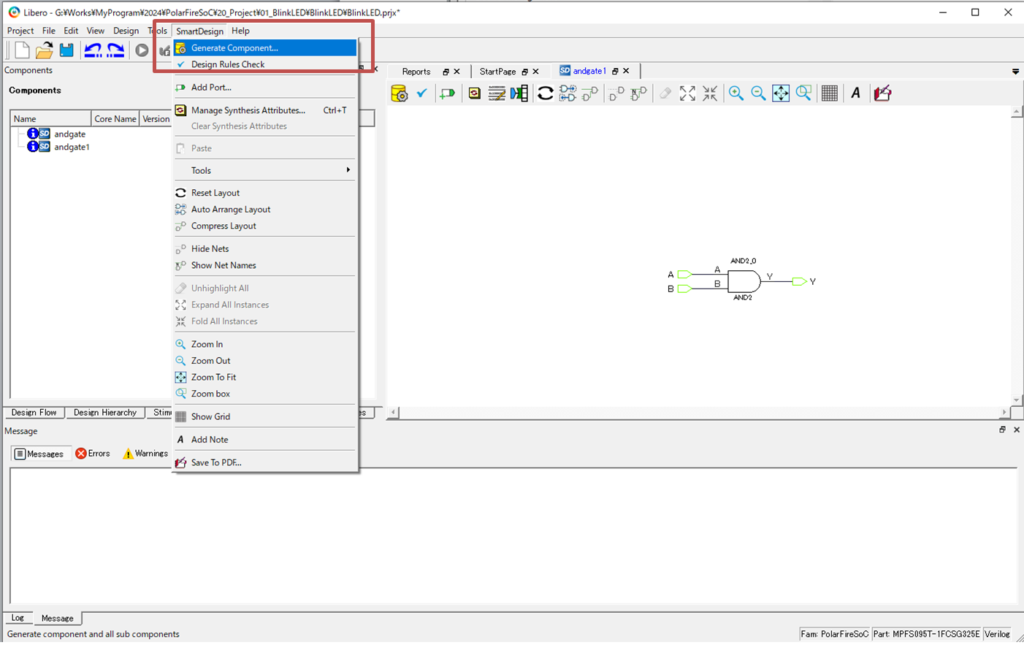

⑤Smart Design から「Genarate Component」をクリックします。

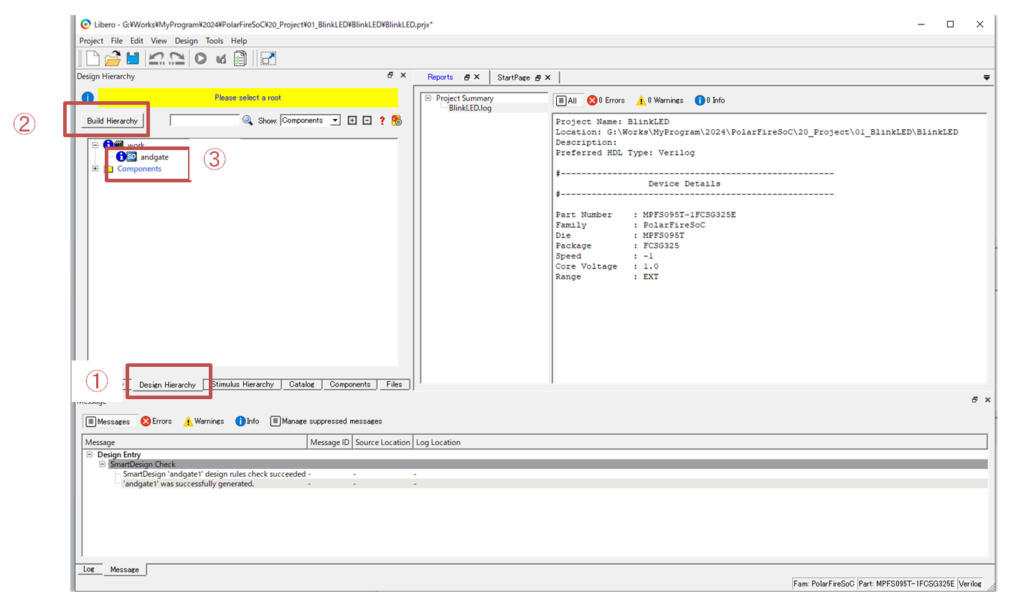

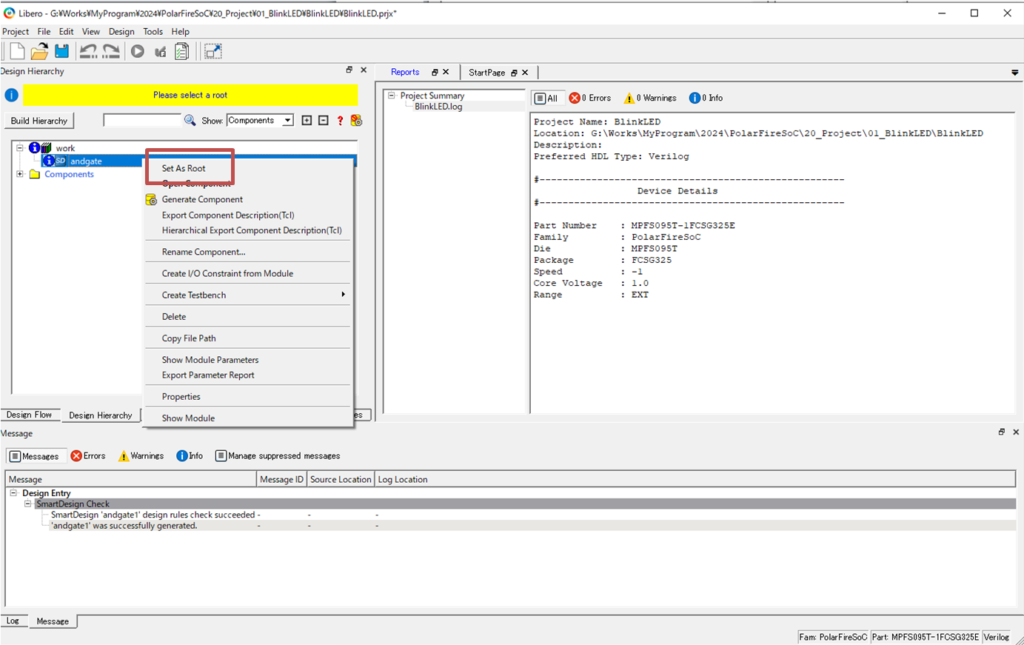

⑥ Design Hierarchyタブを選択し「Build Hierarchy」をクリック後、「andgate」を右クリックします。

⑦「Set As Root」をクリックします。

3.デザインの合成

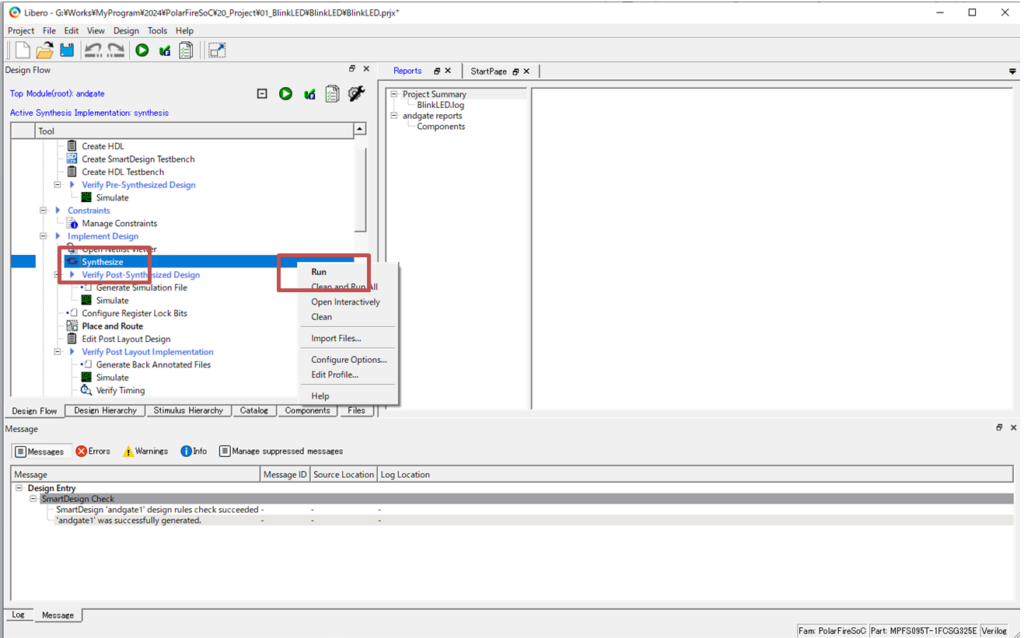

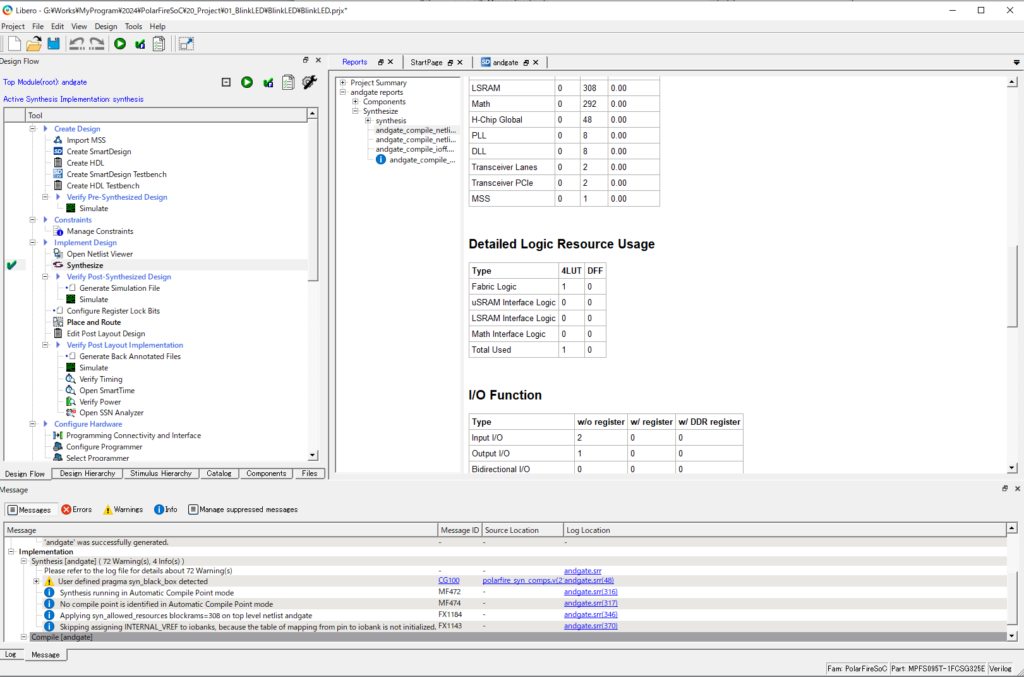

①Dedign Flowタブの「Implement Design > Synthesize」を右クリックし「Run」をクリックします。

②合成が完了すると、左の「Synthesize」にチェックアイコンが付きます。

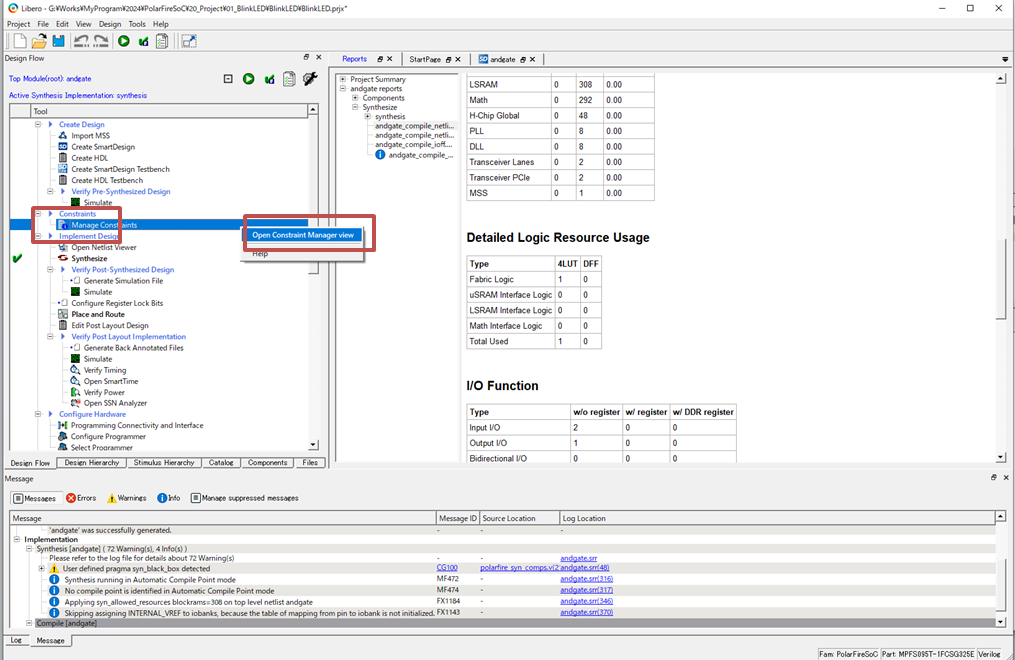

③Dedign Flowタブの「Constraints > Manage Constraints」を右クリックし、メニューから「Open Constraint Manager view」をクリックします。

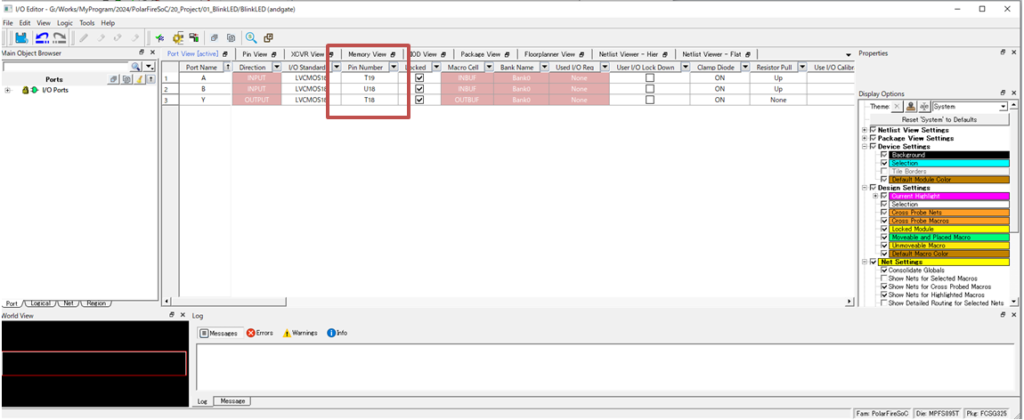

④I/O Editorが立ち上がりますので、下記のようにPin Numberを設定します。

| Port Name | Pin Number |

| A | T19 |

| B | U18 |

| Y | T18 |

⑤設定後は「File > Exit」をクリック後、保存して終了します。

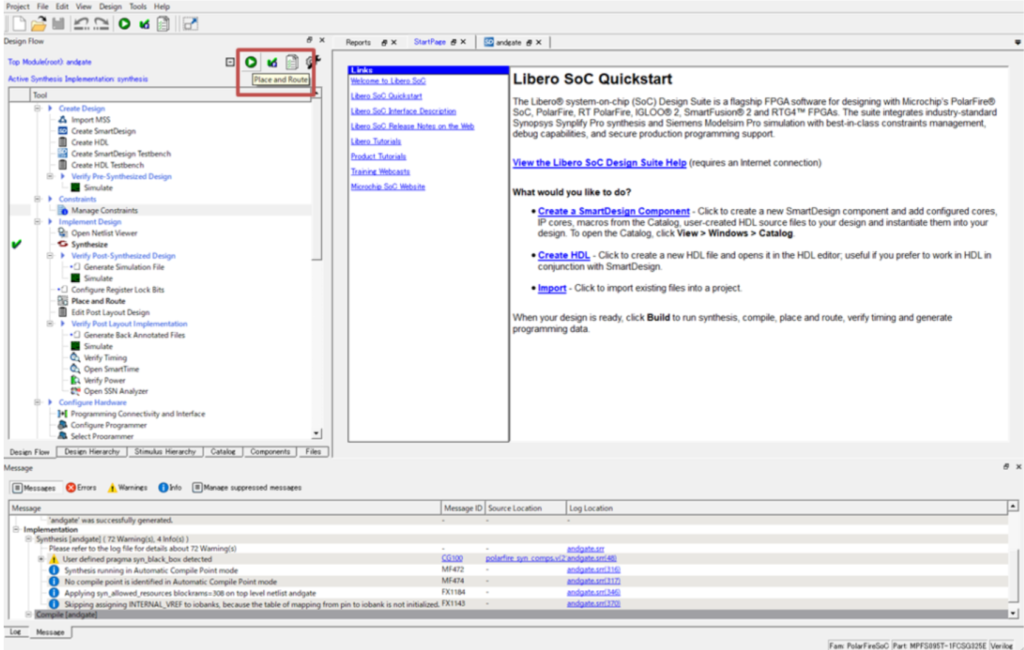

⑥「Design Flow」タブの上部の再生アイコンをクリックすると、配置、配線が行われます。

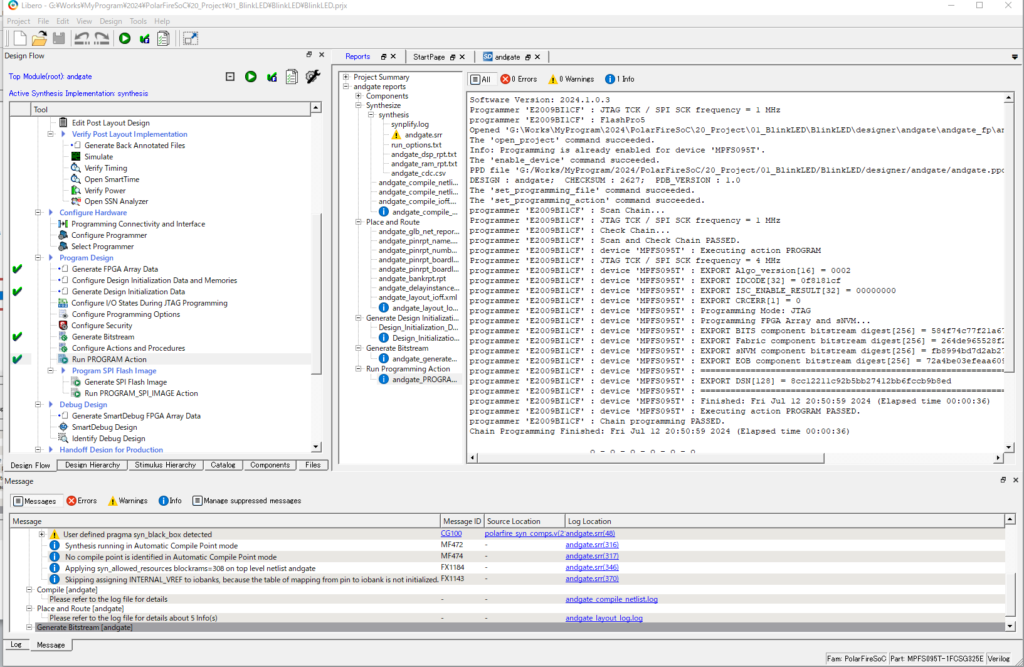

4.書込み

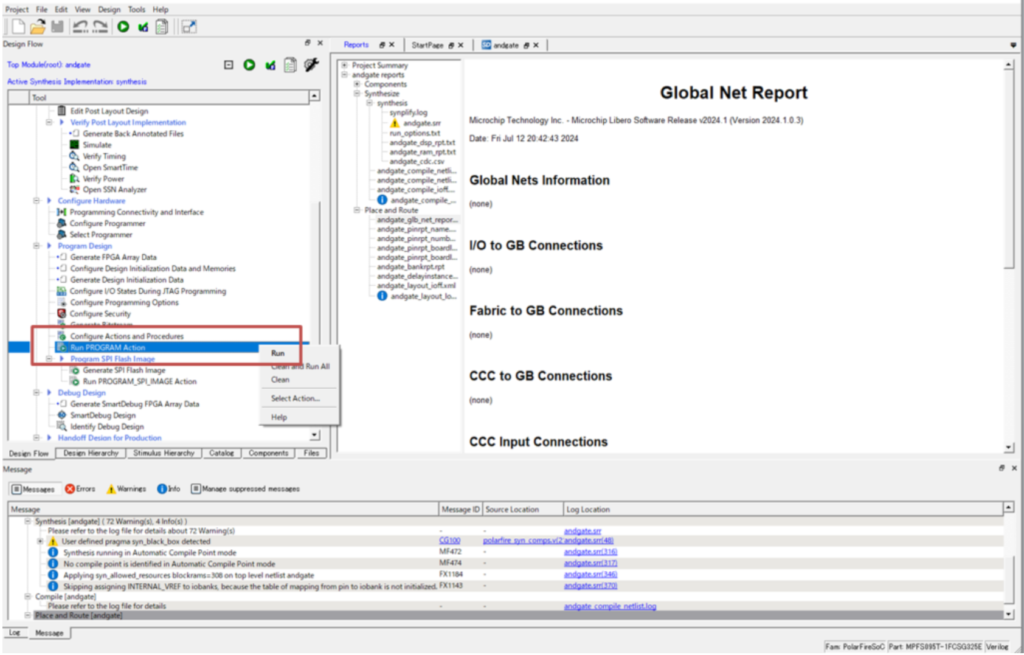

①「Design Flow」タブの「Run PROGRAM Action」を右クリック後、メニューから「Run」を選択

②書き込みが完了するまで待機します。完了すると以下のようなメッセージが表示されます。

5.動作確認

これで基板上のSW1かSW2のどちらかを押すとLED1が消灯することが確認できると思います。

Lチカまでの道のり③

最後に1秒間隔でLED1を点滅させるプロジェクトを作成します。

1.プロジェクト作成

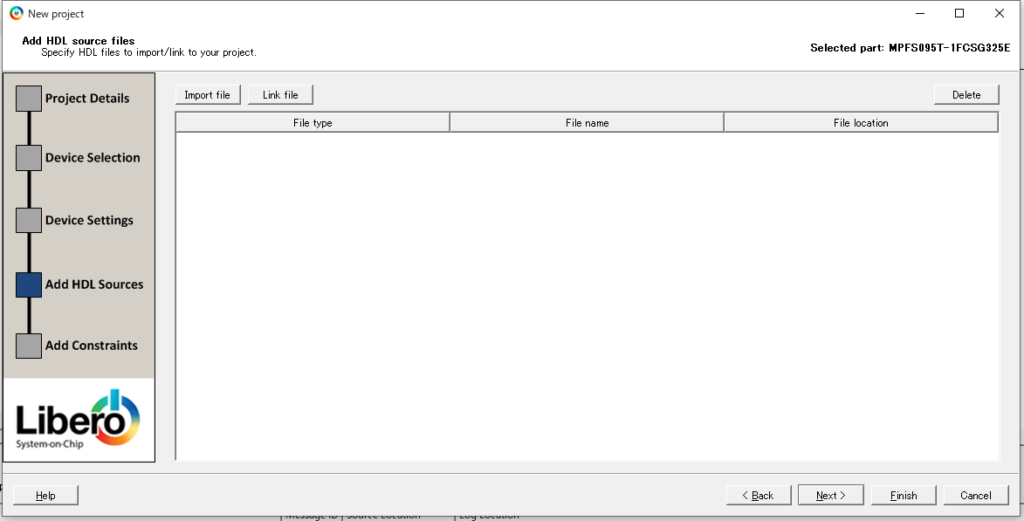

①プロジェクトを生成し「NEXT」をクリック

②MPFS095T-1FCSG325Eを選択し「NEXT」をクリック

③下記のように設定し「NEXT」をクリック

| 項目 | 値 |

| Core Voltage | 1.0 |

| Default I/O technology | LVCMOS 1.8V |

| Reserve pin for probes | チェック オン |

| System controller suspended mode | チェック オフ |

④「Finish」をクリック

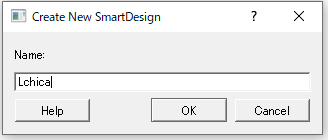

⑤Dedign Flowタブの「Create SmartDesign」をダブルクリック

⑥Create New SmartDesignダイアログのNameに「Lchica」と入力しOKをクリック

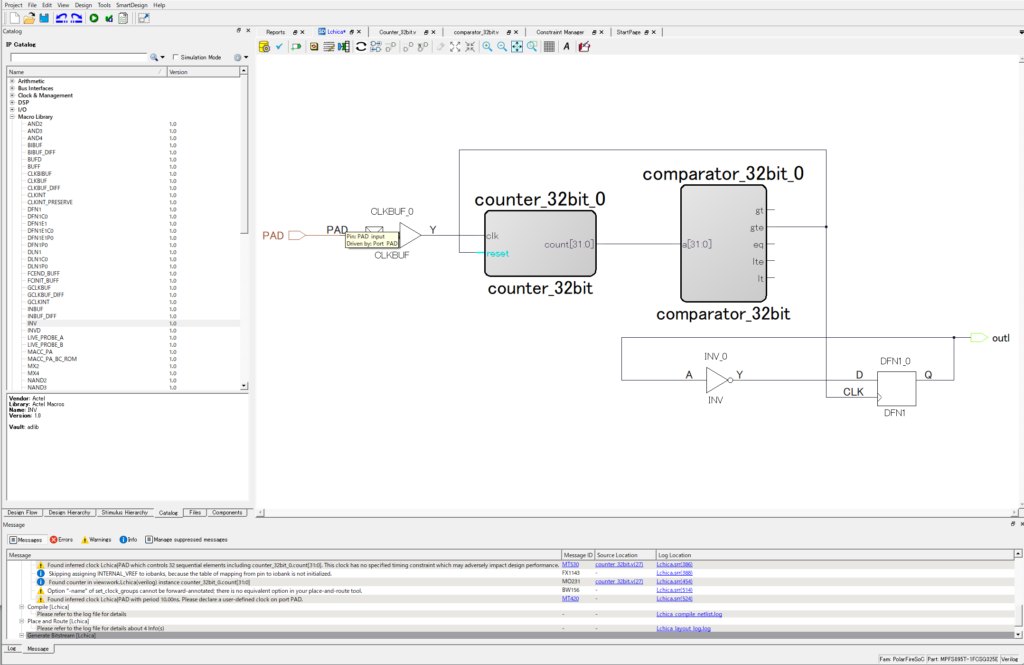

2.VHDLデザインの作成

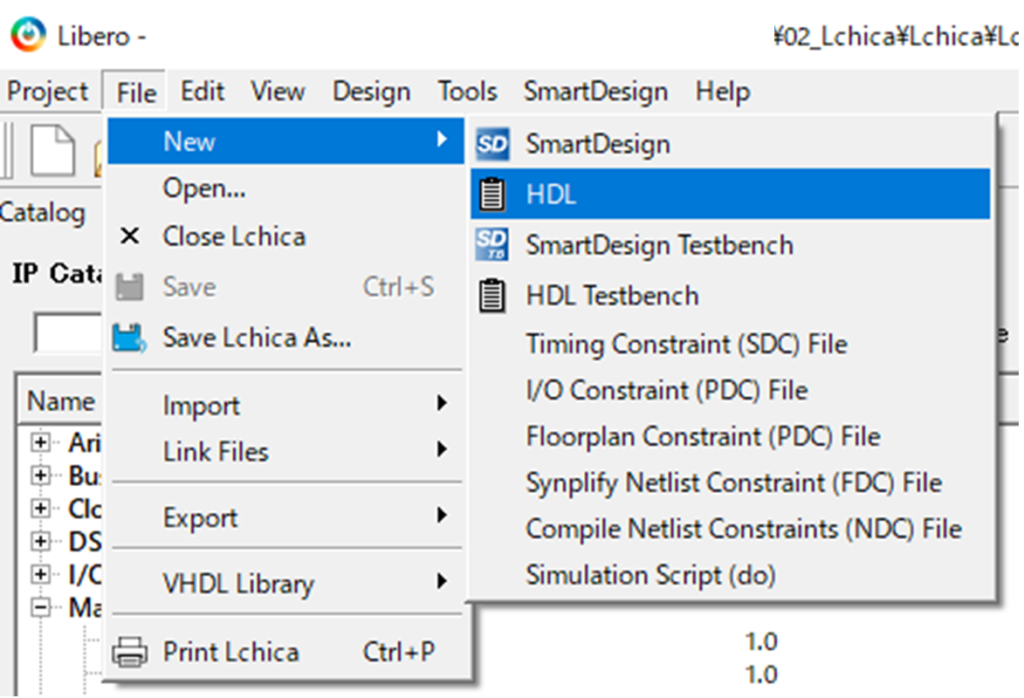

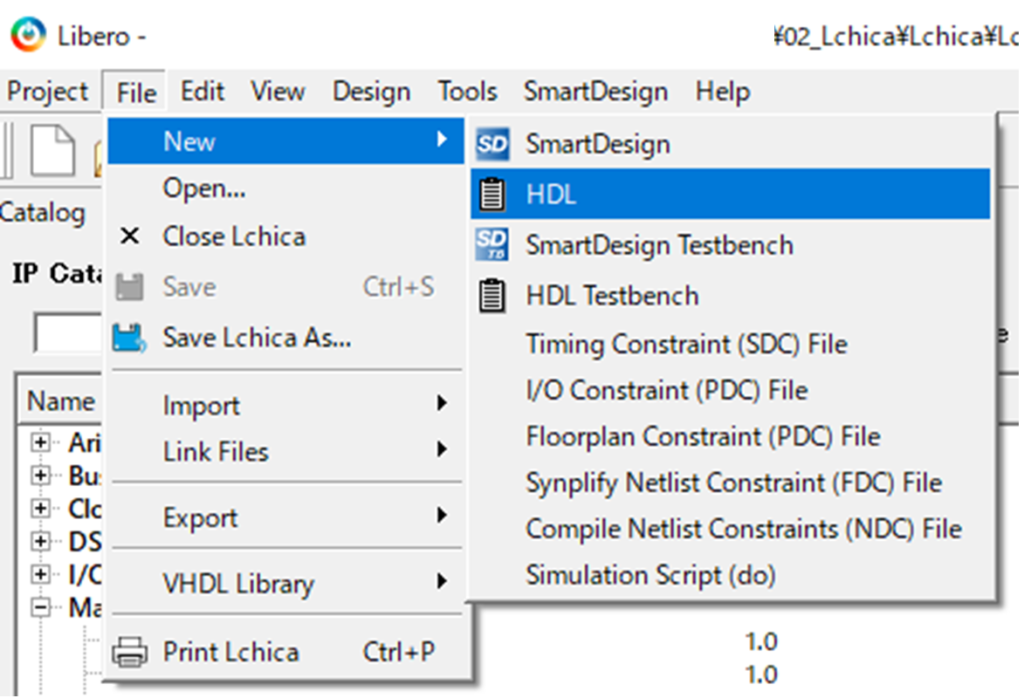

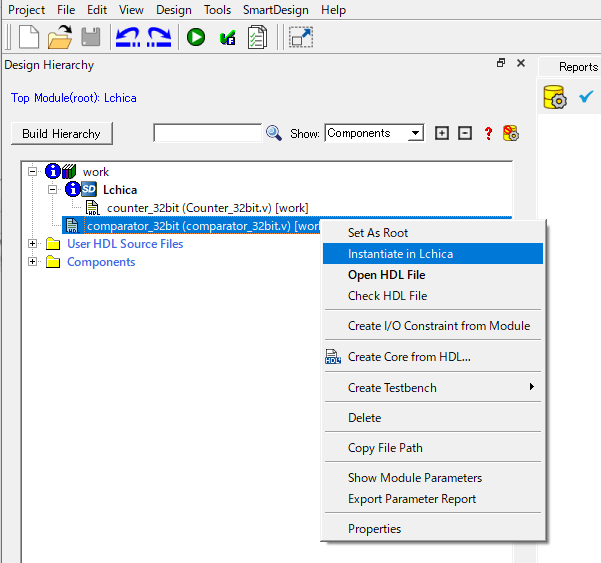

①「File > New >HDL」の順にクリック

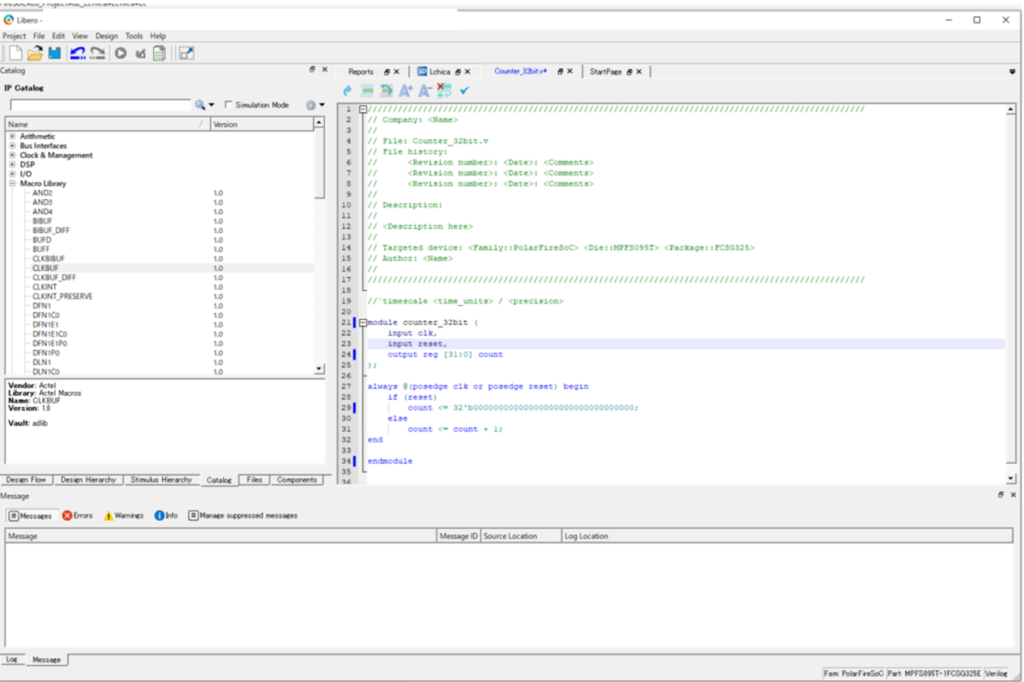

②HDLtypeをVeriloghに選択、Nameを「Counter_32bit」と入力し「OK」をクリック

③エディター画面に下記コードをペーストし保存

module counter_32bit (

input clk,

input reset,

output reg [31:0] count

);

always @(posedge clk or posedge reset) begin

if (reset)

count <= 32'b00000000000000000000000000000000;

else

count <= count + 1;

end

endmodule

⑤「File > New >HDL」の順にクリック

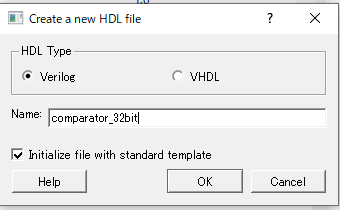

⑥HDLtypeをVeriloghに選択、Nameを「comparator_32bit」と入力し「OK」をクリック

③エディター画面に下記コードをペーストし保存します。

module comparator_32bit(

input [31:0] a,

output reg gt, // greater than (a > b)

output reg gte, // greater than or equal to (a >= b)

output reg eq, // equal (a == b)

output reg lte, // less than or equal to (a <= b)

output reg lt // less than (a < b)

);

parameter [31:0] FIXED_VALUE = 32'h02FAF080; // 32-bit fixed value

always @(*) begin

// Initialize outputs

gt = 0;

gte = 0;

eq = 0;

lte = 0;

lt = 0;

// Perform comparisons

if (a > FIXED_VALUE) begin

gt = 1;

gte = 1;

end else if (a < FIXED_VALUE) begin

lt = 1;

lte = 1;

end else begin

eq = 1;

gte = 1;

lte = 1;

end

end

endmodule3.論理回路の作成

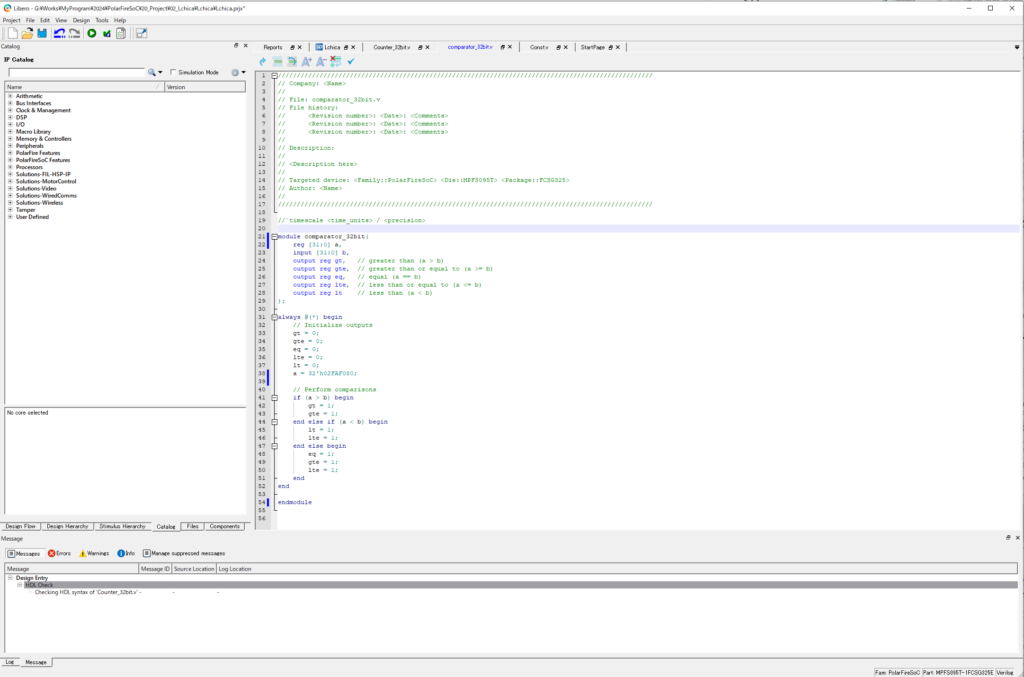

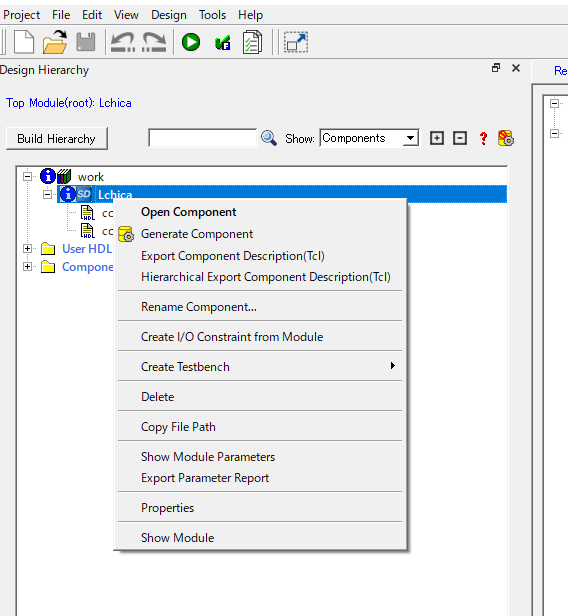

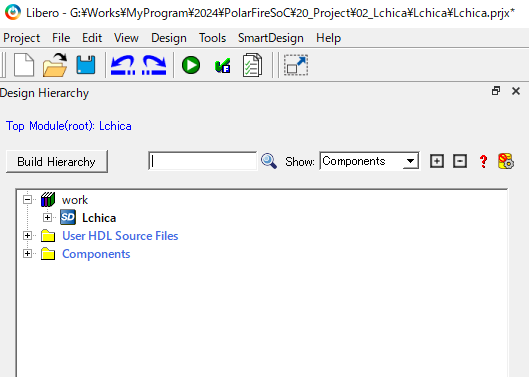

①Design Hierarchyタブを選択し「Build Hierarchy」をクリック後、「Lchica」を右クリックし、「Set As Root」をクリックします。

②作成したVerilogを右クリックし、「Instantiate in Lchica」をクリックします。

③カウンターとコンパレータが追加されますので、更に「CLKBUF」「INV」「DFN1」を追加後、下記のように接続し、保存します。

④Lchicaを右クリックし「Generate Component」をクリック

⑤Build Hierarchyをクリック

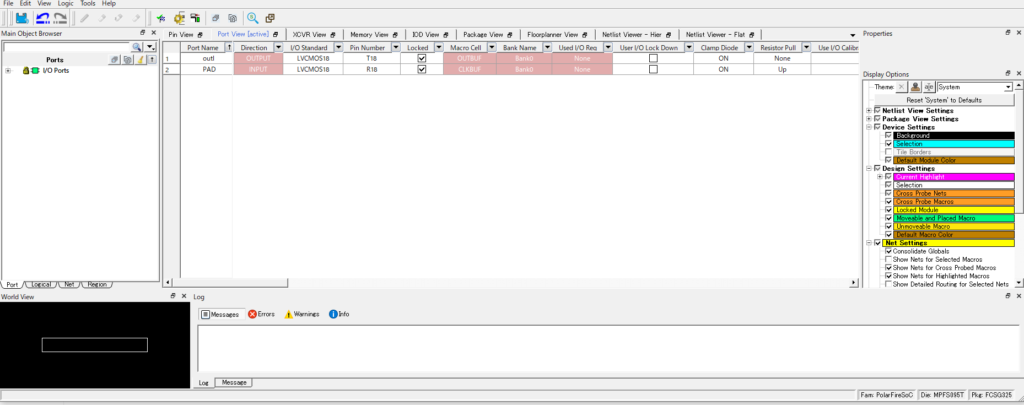

4.デザインの合成

①Dedign Flowタブの「Implement Design > Synthesize」を右クリックし「Run」をクリックします。

③Dedign Flowタブの「Constraints > Manage Constraints」を右クリックし、メニューから「Open Constraint Manager view」をクリックします。

outlをT18、PADをR18に設定し保存後ウィンドウを閉じます。

④「Design Flow」タブの上部の再生アイコンをクリックすると、合成が行われます。

⑤「Design Flow」タブの「Run PROGRAM Action」を右クリック後、メニューから「Run」を選択

⑥書き込みが完了するまで待機します。完了すると以下のようなメッセージが表示されます。

5.結果

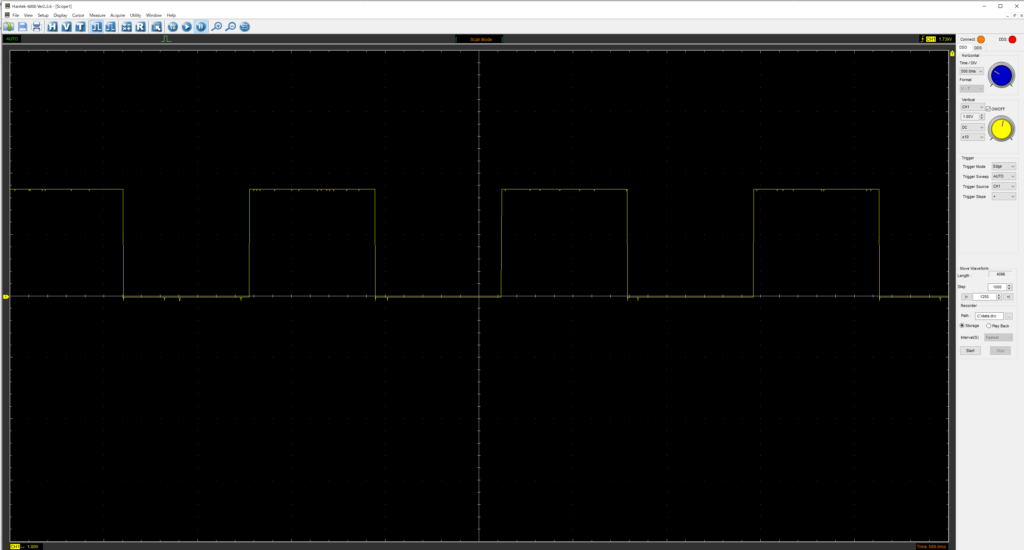

チップ抵抗R699の方端をオシロスコープで確認すると1秒間隔でトグルしている事がわかります。

コメント