はじめに

1.概要

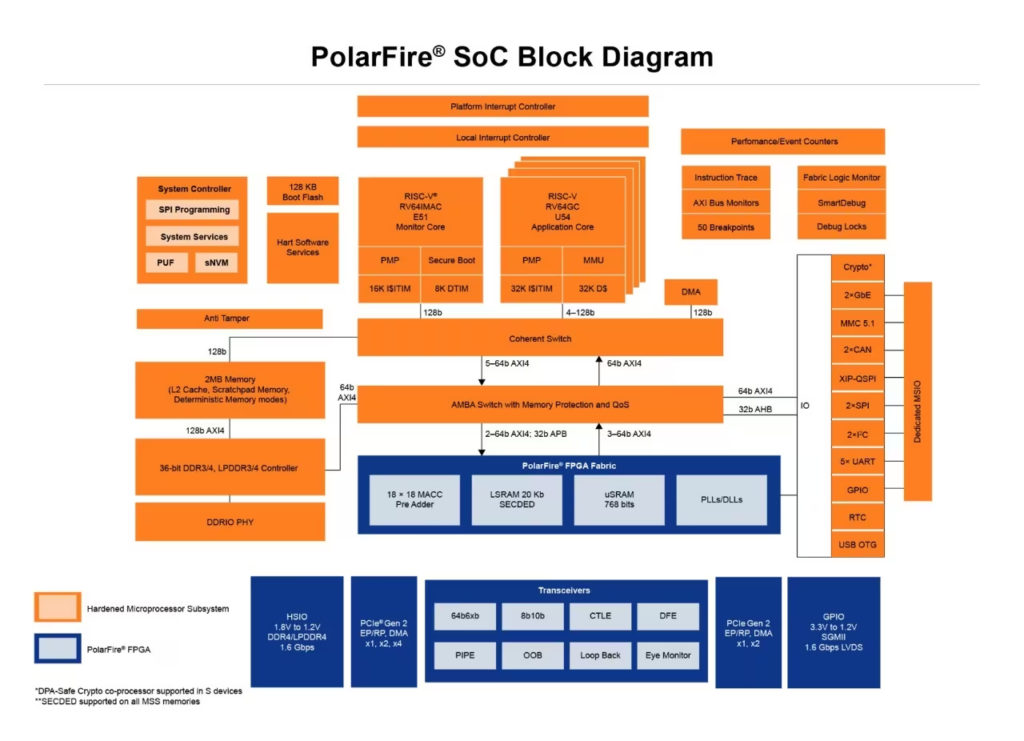

Microchip社のPolarFire® SoCは、不揮発性で低消費電力のミッドレンジSoC FPGAで、64ビットのRISC-V ISAを5コア搭載したプロセッサーと低消費電力FPGAを組み合わせたチップです。

外部リンク

| タイトル | リンク |

| PolarFire SoCプロダクトページ (Microchip) | PolarFire® SoC FPGAs | Microchip Technology |

| PolarFire SoC Discoveryキット (Microchip) | PolarFire® SoC Discovery Kit | Microchip Technology |

| PolarFire SoC MSS テクニカルリファレンスマニュアル | PolarFire SoC MSS Technical Reference Manual (microchip.com) |

| Microprocessor Subsystem (MSS) User’s Guide | PolarFire SoC MSS Technical Reference Manual (microchip.com) |

| PolarFire SoCプロダクトページ (GitHub) | PolarFire-SoC · GitHub |

| ベアメタルプロジェクト (Github) | GitHub – polarfire-soc/polarfire-soc-bare-metal-examples: Bare metal example software projects for PolarFire SoC |

| GPIO Bare Metal Driver (Github) | polarfire-soc-documentation/bare-metal-embedded-software/bare-metal-driver-user-guides/polarfire-soc-mss-driver-user-guides/mss-gpio/mss-gpio-driver-user-guide.md at master · polarfire-soc/polarfire-soc-documentation · GitHub |

2.この記事の目的

この記事は私の忘備録も兼ねて、PolarFire®SoCのMSS(Microprocessor Subsystem)にてLチカが出来る事を目指しています。試行錯誤で実験を進めておりますので、記事の不備とうご容赦ください。

3.構成

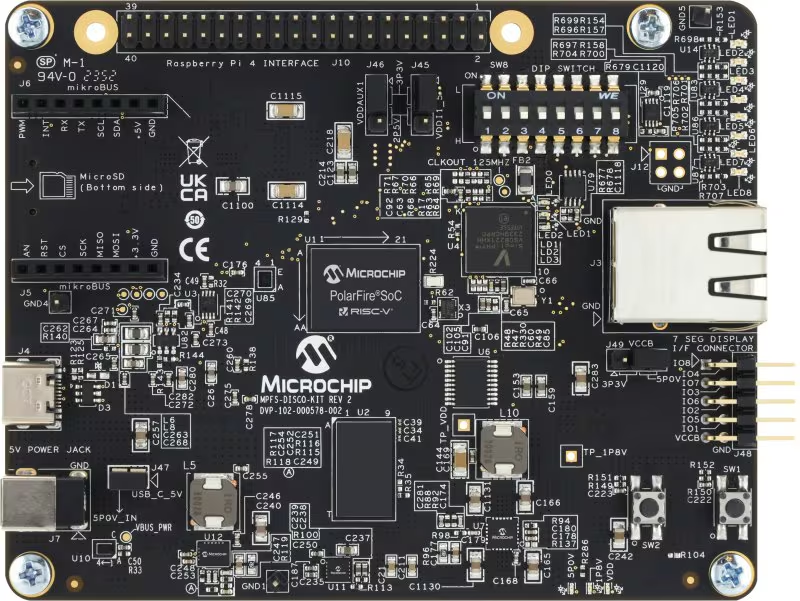

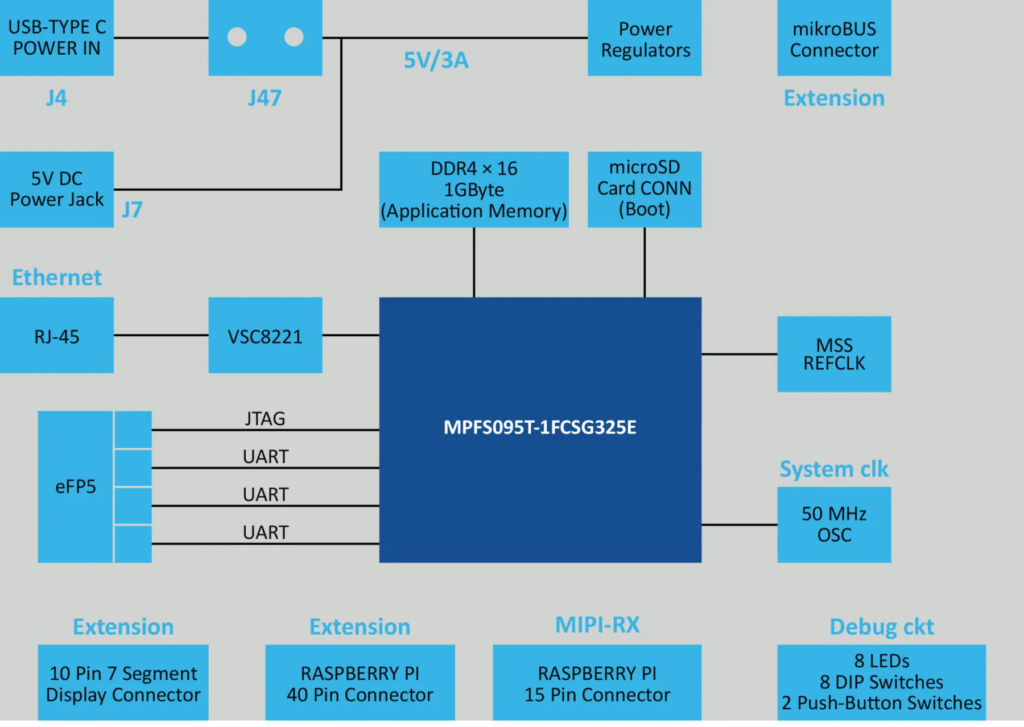

前回の記事と同じく、PolarFire® SoC Discovery Kitを使用し、動作を確認していきます。

PolarFire® SoC Discovery Kit | Microchip Technology

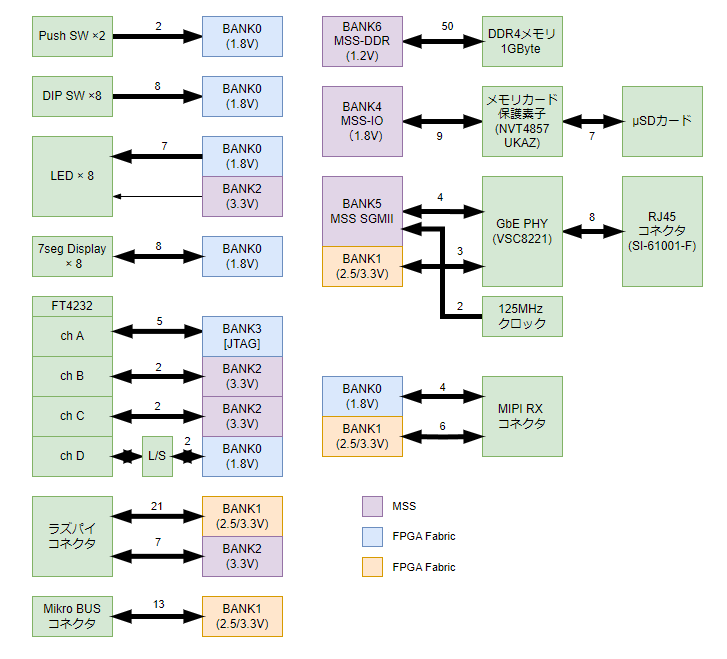

下記に各BANKの接続図を示します。

Lチカまでの道のり①

0.はじめに

GitHubにPolarFire SoCに関するリポジトリが公開されています。

PolarFire-SoC · GitHub

リポジトリには以下のような関連リソースがありますので、まずはLチカの前にGitHubにアップされているベアメタルExamplesを動かしてみます。

1.Gitからダウンロード

下記のGitHubからベアメタルサンプルプロジェクトをダウンロード&解凍を行います。

2.プロジェクトを開く

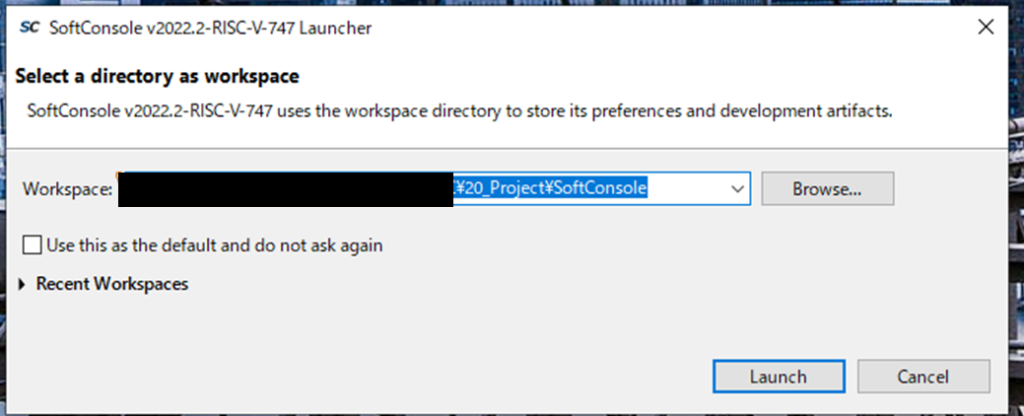

①SoftConsoleアプリケーションを起動すると、最初にワークスペースの保存場所を聞かれるので、ディレクトリを指定します。

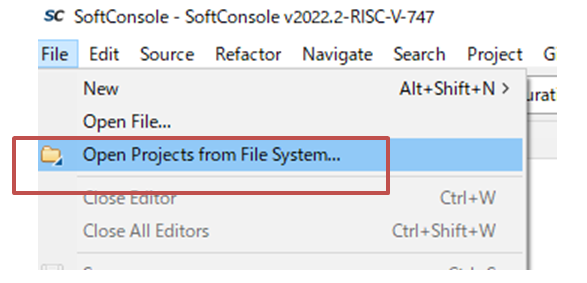

②File > Open Project from File System をクリックします。

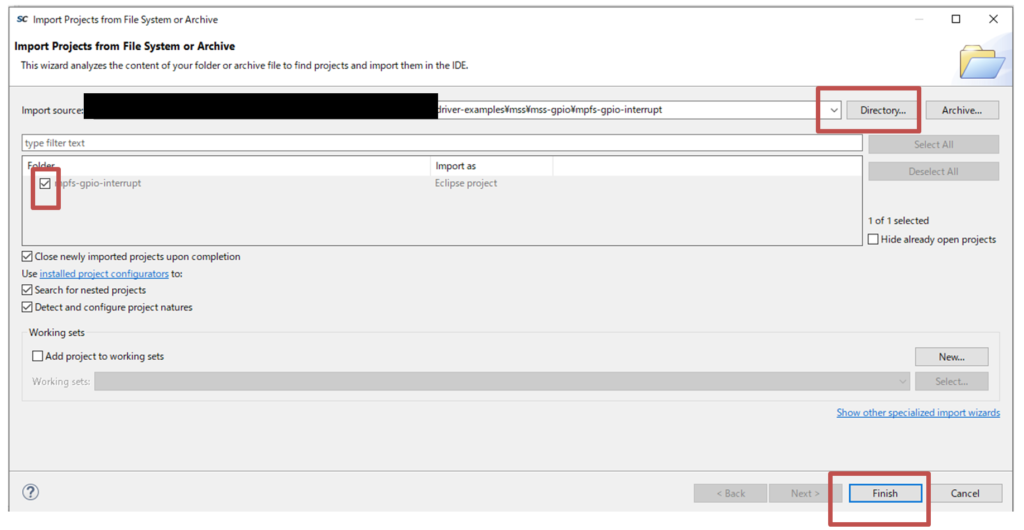

③「Directort..」ボタンを押し、Githubからダウンロードした「mpfs-gpio-interrupt」フォルダを指定します。中間のチェックボックスにチェックを入れ、最後に「Finish」ボタンを押します。

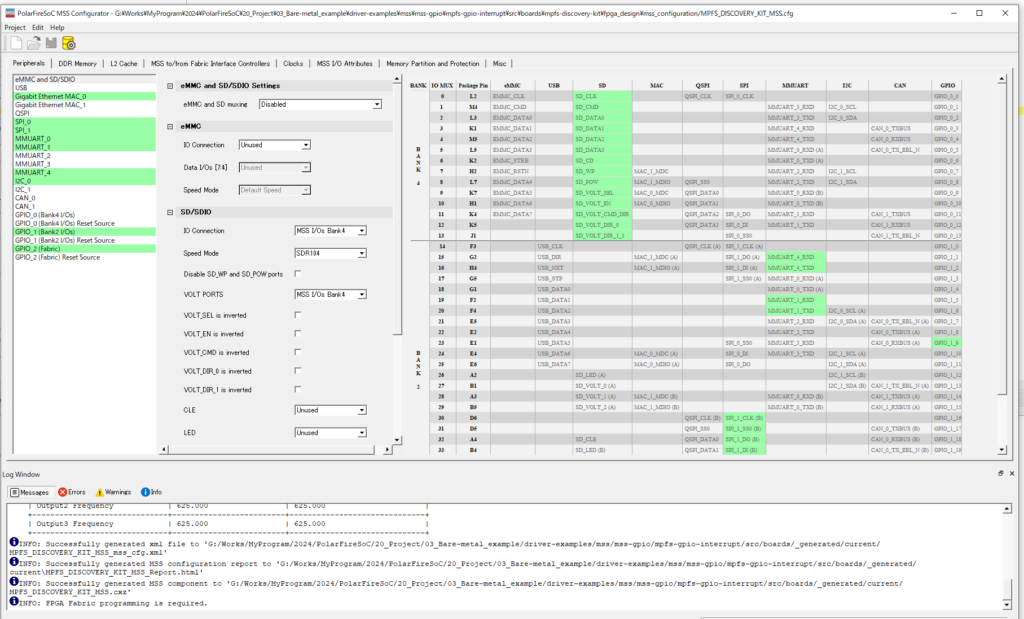

3.プロジェクトの設定

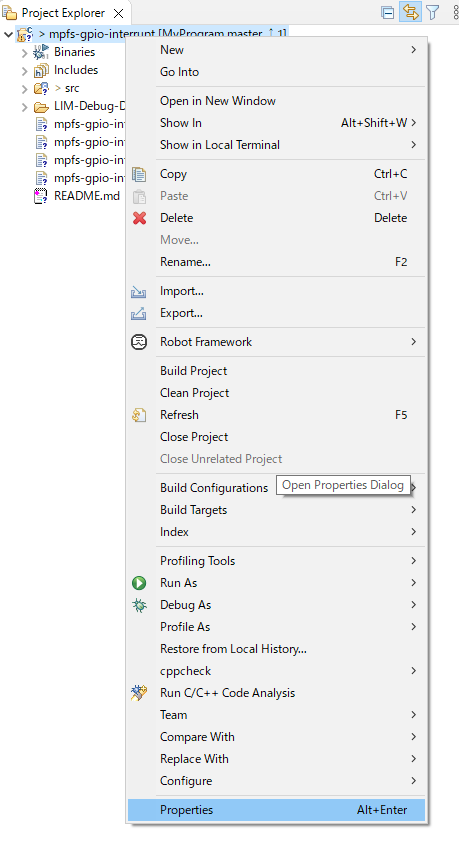

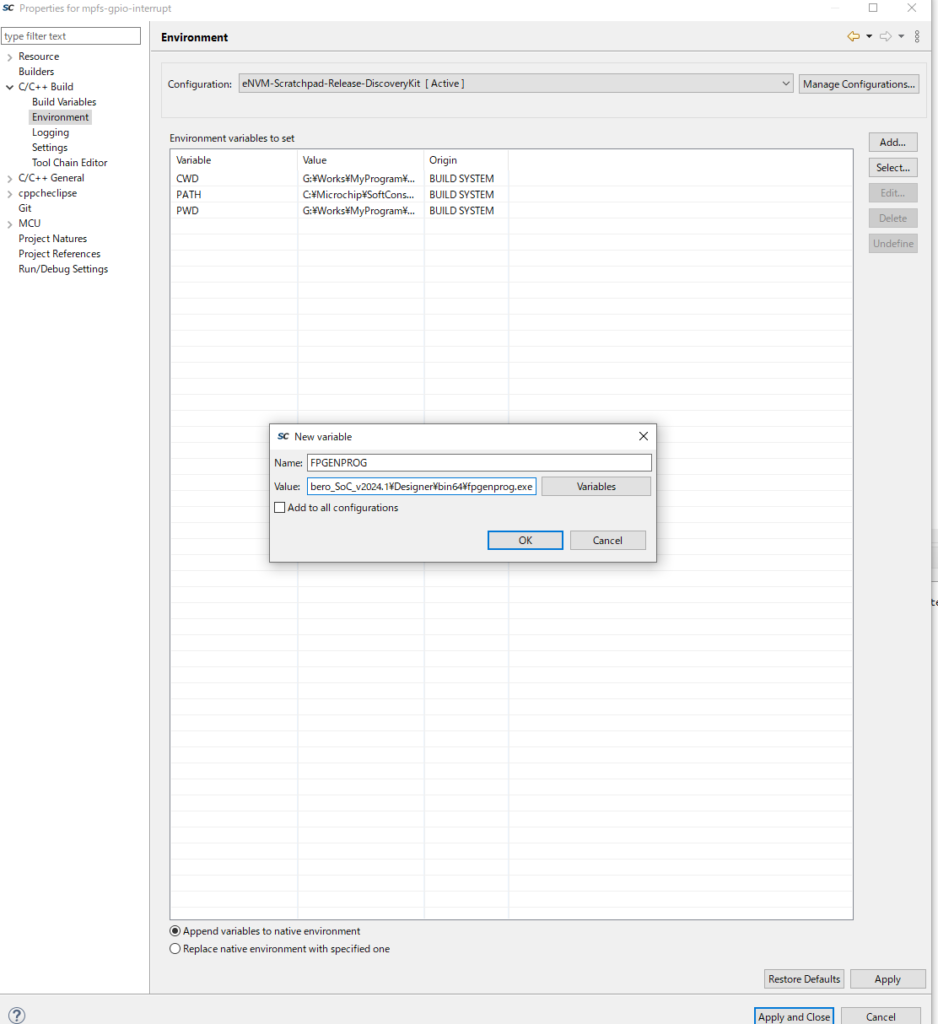

①プロジェクトを右クリックし、「Properties」を選択

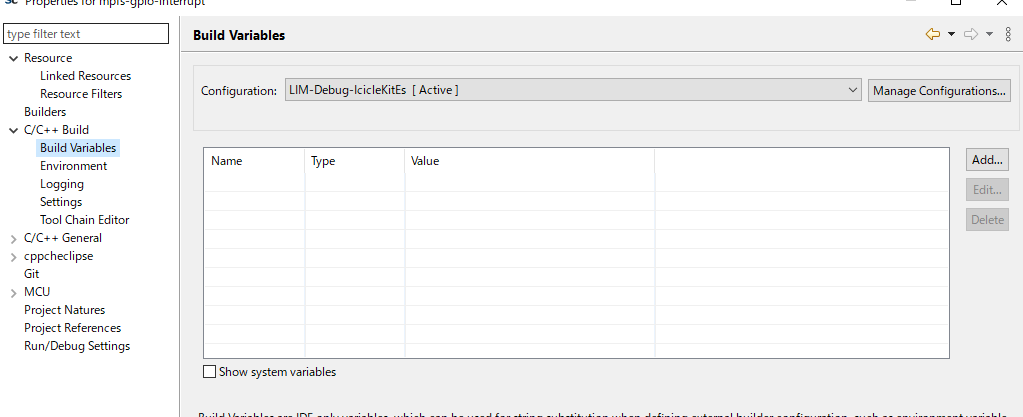

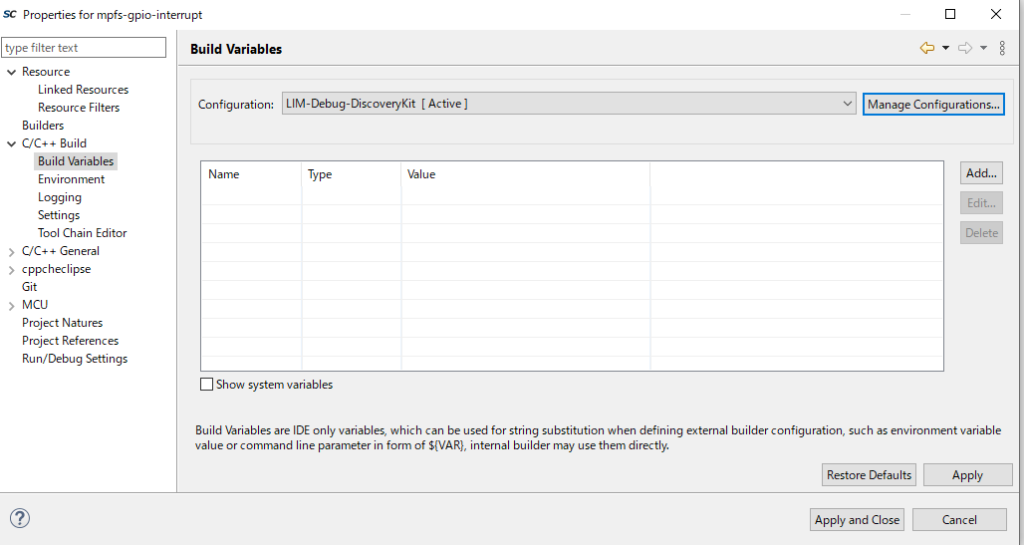

②「C/C++ Builld 」 から「Build Variables」を選択します。

Configrationが「LIM-Debug-DiscoveryKit[Active]」になっていない場合、「Manage Configuration」ボタンを押します。

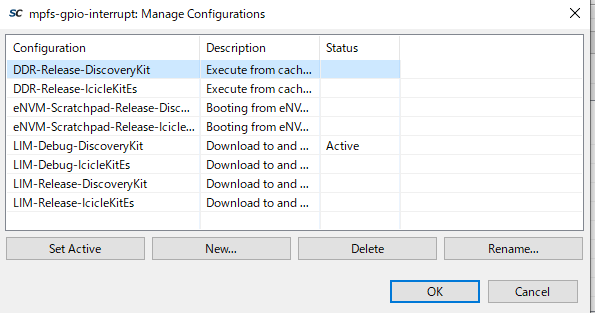

③LIM-Debug-DiscoveryKitを選択し「Set Active」ボタンを押します。

④「Apply」ボタンを押します。

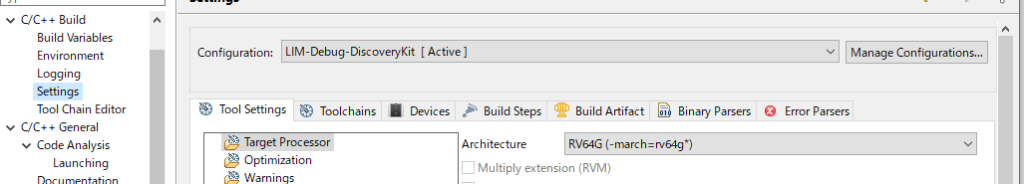

⑤「C/C++ Builld 」 から「Setting」を選択し、Configrationが「LIM-Debug-DiscoveryKit[Active]」になっていることを確認します。

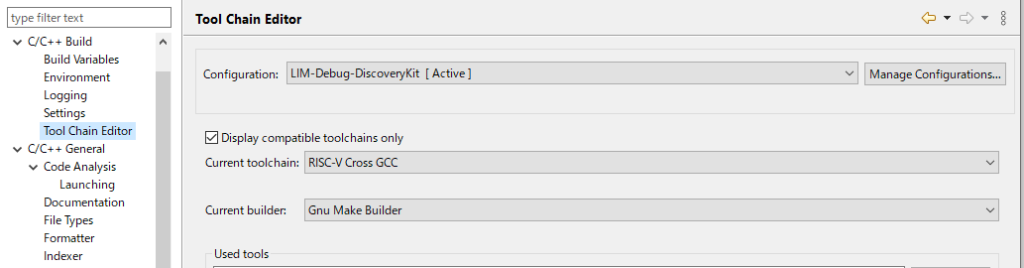

⑥「C/C++ Builld 」 から「Tool Chain Editor」を選択し、Configrationが「LIM-Debug-DiscoveryKit[Active]」になっていることを確認します。

⑦「Apply and Close」をクリックし、ウィンドウを閉じます。

4.ソースファイルの変更

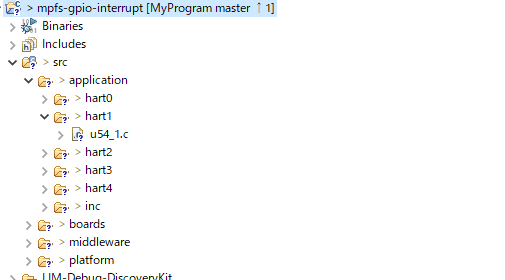

①src > application > hart1 > u54_1.cをダブルクリックで開きます。

②125行目あたりに//ここから挿入 ~ //ここまでをペーストします。

SYSREG->GPIO_INTERRUPT_FAB_CR = 0xFFFFFFFFUL;

PLIC_SetPriority_Threshold(0);

for (int_num = 0u; int_num <= GPIO2_NON_DIRECT_PLIC; int_num++)

{

PLIC_SetPriority(GPIO0_BIT0_or_GPIO2_BIT0_PLIC_0 + int_num, 2u);

}

//ここから挿入

uint64_t led_cnt;

MSS_GPIO_config(GPIO1_LO, MSS_GPIO_9, MSS_GPIO_OUTPUT_MODE);

while(1u)

{

led_cnt ++;

if (led_cnt < 500000)

{

MSS_GPIO_set_output(GPIO1_LO, MSS_GPIO_9, 1u);

// led_cnt = 1;

}

else if (led_cnt < 1000000)

{

MSS_GPIO_set_output(GPIO1_LO, MSS_GPIO_9, 0u);

// led_cnt = 0;

}

else

{

led_cnt = 0;

}

}

//ここまで

MSS_GPIO_init(GPIO2_LO);

for (cnt = 9u; cnt< 23u; cnt++)

{

MSS_GPIO_config(GPIO2_LO,

cnt,

MSS_GPIO_OUTPUT_MODE);

}

MSS_GPIO_config(GPIO2_LO, MSS_GPIO_26,5.Debug

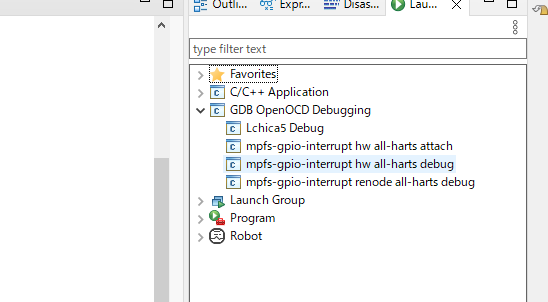

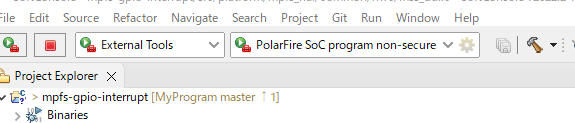

①ワークスペースの右にある、「Launch Configration」タブから、「GDB OpenOCD Debugging」をクリックし「mpfs-gpio-interrupt hw all-harts debug」をダブルクリックし、実行します。

6.結果

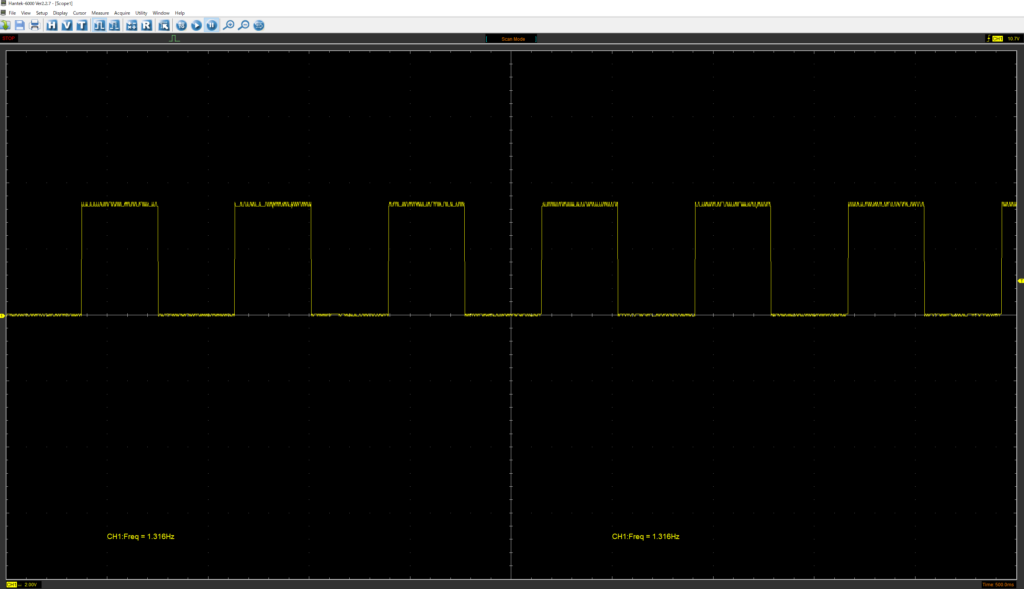

チップ抵抗R705の方端をオシロスコープで確認すると376msecでトグルしている事がわかります。

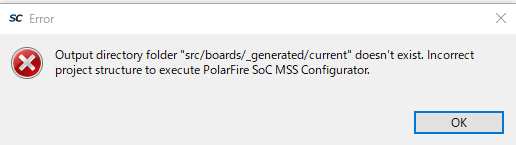

7.プログラミング

(以下の記事は書きかけです)

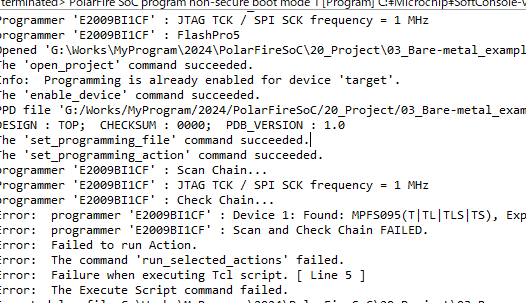

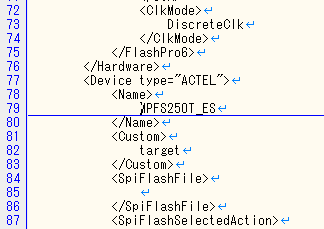

Opened ‘G:\Works\MyProgram\2024\PolarFireSoC\20_Project\03_Bare-metal_example\driver-examples\mss\mss-gpio\mpfs-gpio-interrupt\eNVM-Scratchpad-Release-DiscoveryKit\bootmode1\fpgenprogProject\proj_fp\proj_fp.pro’

The ‘open_project’ command succeeded.

Info: Programming is already enabled for device ‘target’.

The ‘enable_device’ command succeeded.

PPD file ‘G:/Works/MyProgram/2024/PolarFireSoC/20_Project/03_Bare-metal_example/driver-examples/mss/mss-gpio/mpfs-gpio-interrupt/eNVM-Scratchpad-Release-DiscoveryKit/bootmode1/fpgenprogProject/proj_fp/target.ppd’ has been loaded successfully.

DESIGN : TOP; CHECKSUM : 0000; PDB_VERSION : 1.0

The ‘set_programming_file’ command succeeded.

The ‘set_programming_action’ command succeeded.

programmer ‘E2009BI1CF’ : Scan Chain…

Programmer ‘E2009BI1CF’ : JTAG TCK / SPI SCK frequency = 1 MHz

programmer ‘E2009BI1CF’ : Check Chain…

Error: programmer ‘E2009BI1CF’ : Device 1: Found: MPFS095(T|TL|TLS|TS), Expected: MPFS250T_ES

Error: programmer ‘E2009BI1CF’ : Scan and Check Chain FAILED.

Error: Failed to run Action.

Error: The command ‘run_selected_actions’ failed.

Error: Failure when executing Tcl script. [ Line 5 ]

Error: The Execute Script command failed.

編集後記

正直なところ、まだわからないことが多く、手探りで実験を進めている状態です。ドキュメントは多く揃っているものの、その分資料やページの量が膨大で初めて扱う内容も多いため、情報の整理に苦労しています。

コメント

はじめまして。

Microchip(Microsemi)のFPGA関連の情報が少なすぎて茫然とする中、こちらにたどり着きました。

この記事のmssでのLチカは、ハード側の構成情報(zynqだと、最初にvivadoでブロックを組むやつ)は要らないのでしょうか。また、Debug実行するときに、SoCに事前に何かをプログラムしておく必要はないのでしょうか。

こんにちは。回答が遅くなりました。

なかなか日本語情報が少なくて苦労しますよね。

私もPolarFireに手を出し始めたばかりで、手探り状態です。

今回の手順を実行すればとりあえずデバッグモードで動作したため、

CPUだけを動かすだけであればFPGA側への書込みは不要だと思います。