概要

以前の記事でCLCモジュールの使い方を説明しました。

CLCモジュールの使い方 – ぴくおの電子工作的な何かWP (electricpico.com)

一般的なロジックICには動作周波数が定められておりHCシリーズでは約17~22MHz,ACシリーズでは約60MHzなどとなっています。これは伝搬遅延時間(tpLH, tpHL)から求められます。

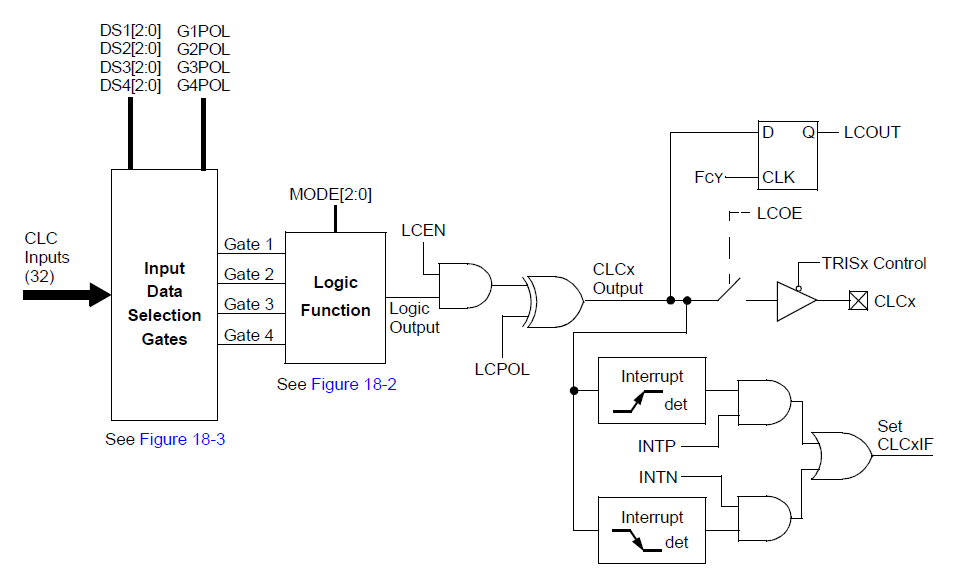

今回はPIC16F1769を用い、入力ピン(CLCIN)に信号を入力し周波数特性を調査しました。一つのCLCユニットは①Input Data Selection Gate②Logic Function③Output と経由しCLCOutピンに接続されています。つまりロジックゲートをいくつも経由して出力されることになります。

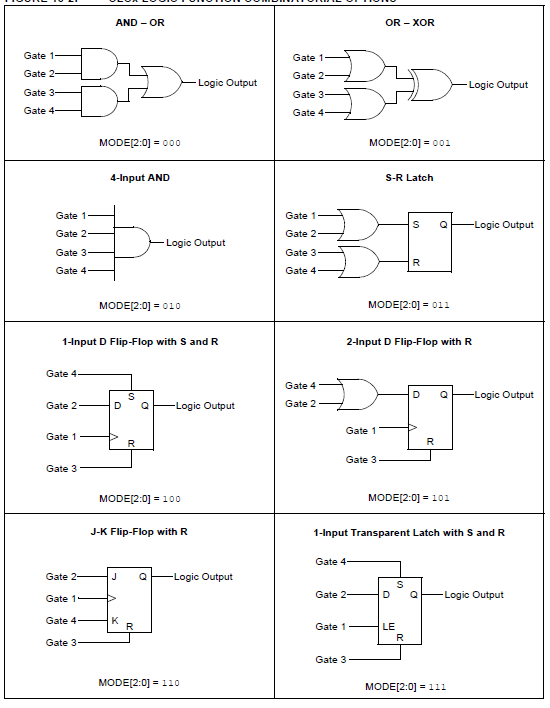

ロジック機能選択ブロックは主に「ゲート」部と「ラッチ」部で構成されます。つまり「カウンタ」などは実質構成できず他のペリフェラル(CCPやNCOなど)と組み合わせ実現させます。

実験構成

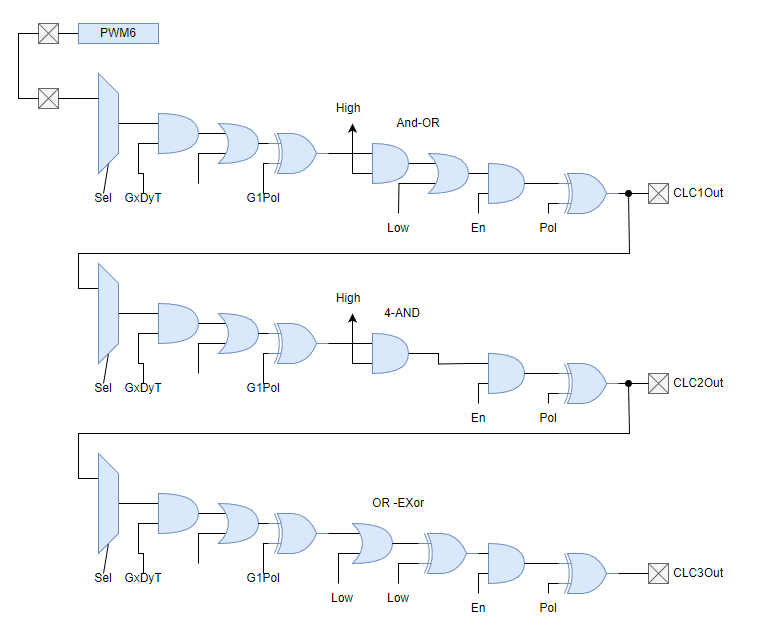

実験構成は以下の通りとし、PWM6出力をCLC1の入力とし次のようにカスケード接続します。

結果

①立ち上がり特性

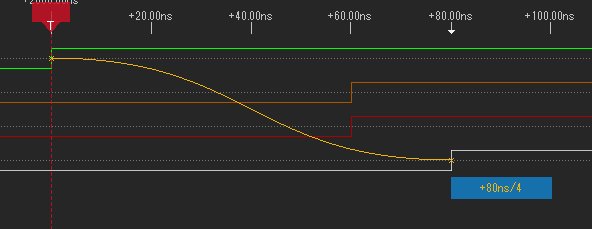

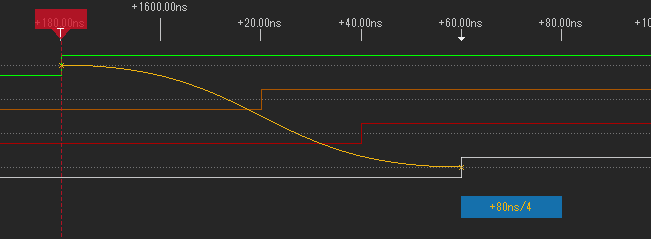

入力(緑)の立ち上がりからオレンジ(CLC1Out),赤(CLC2Out),白(CLC3Out)の差分は以下のとおりで、CLC3の変化まで60~80nsecとなっております。

なおCLC1とCLC2の出力が同時に変化しているのは、ロジックアナライザのサンプルレートが50MHz(分解能が20nsec)で、これ以上細かい時間分解能の変化が捉えられない為です。

②PWM周波数特性

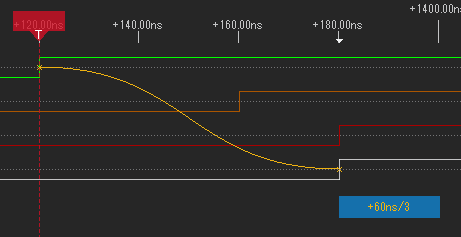

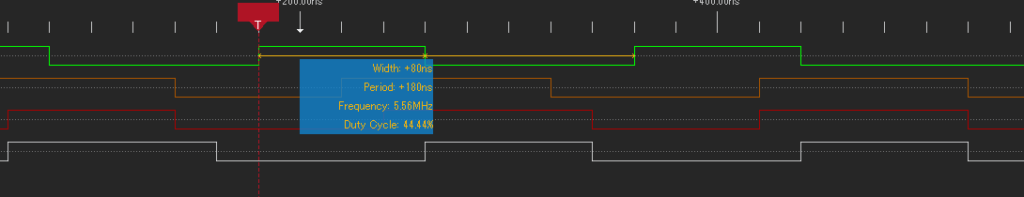

約5MHzのPWM入力では以下の通りで、3段目のCLC3では位相が反転しております。

この結果が遅いと判断するのか速いと判断するのかはアプリケーション次第だとは思いますが、

CLCの1ユニットが複数のロジックで構成されている事を考慮すれば、妥当なラインではないでしょうか?

コメント