概要

dsPIC33Cシリーズの高分解能PWMモジュールは様々なスイッチングアプリケーションに対応できる構成となっています。

今回はスロープ補償機能を試してみます。

スイッチング電源をピーク電流モードで駆動させ、且つPWMのDutyが50%以上の場合に発生する低調波発振という現象を防止する役目。

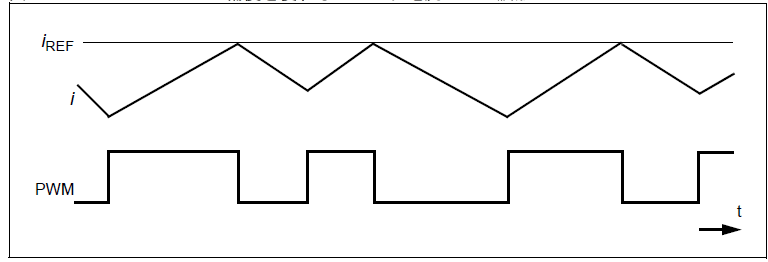

PWMのON後上昇するインダクタ電流 i が閾値 iREFを超えた時にPWMをOFFするピーク電流モードにおいて、スロープ補償を使わないとPWMが低調波で発振します(fig.1)

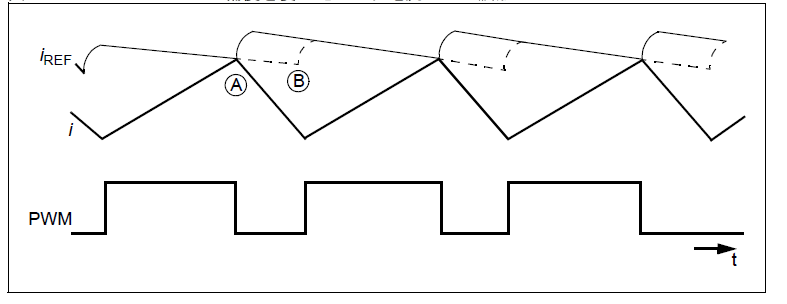

このiREFをPWM開始から徐々に下降させる事で、低調波発振を防止します(fig.2)

■スロープ補償に関して過去の記事

DACモジュールの使い方(三角波出力編) – ぴくおの電子工作的な何かWP (electricpico.com)

■スロープ補償に関しての詳細(外部リンク)

スロープ補償とは?DCDCコンバータのサブハーモニック発振を対策 【Analogista】

サブハーモニック発振の理論解 | スロープの伝達関数とは | TechWeb (rohm.co.jp)

スロープを生成する機能自体は高分解能PWMモジュールではなく、DACモジュールに搭載されておりPWMと連携することでPWMと同期した信号が出力されます。

ハードウェア構成と制御ブロック

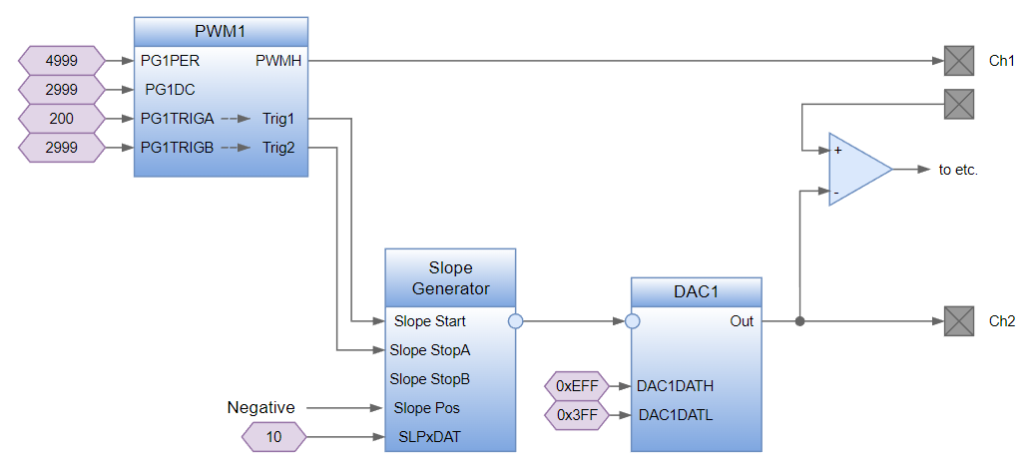

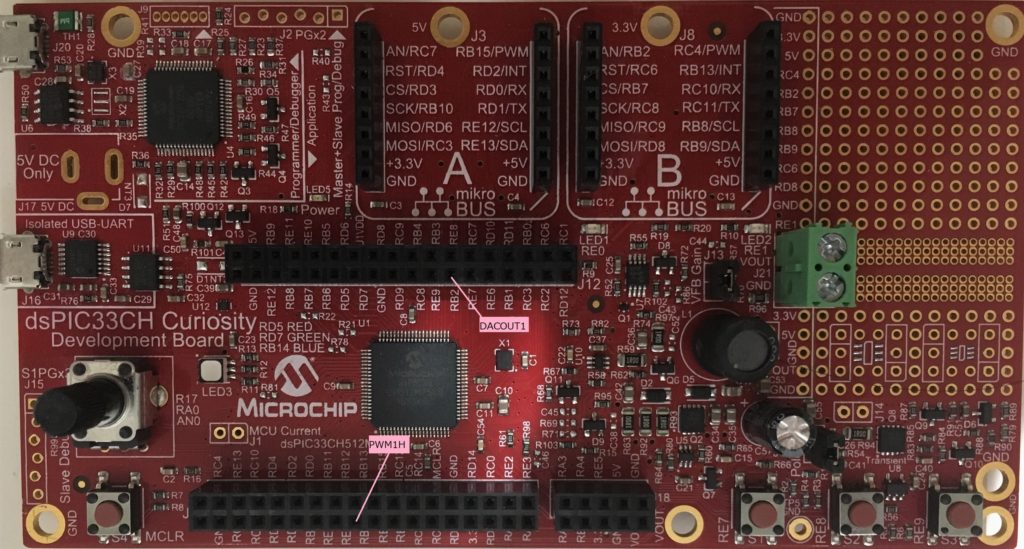

今回のプログラムはPWM1Hに同期したスロープ波形をDAC1モジュールによって生成しDacOutから出力をします。

レジスタ

関連レジスタに関しては非常に多いため、今回の動作に関係する部分だけ抜粋します。

| レジスタ名 | 機能 | 説明 |

| PCLKCON | PWM CLOCK CONTROL REGISTER | PWMクロックを制御 |

| PGxCONL | GENERATOR x CONTROL REGISTER LOW | PGxのクロックや動作モードの設定を行います |

| PGxIOCONH | PWM GENERATOR x I/O CONTROL REGISTER LOW | PGxの出力ピンに関する設定を行います |

| PGxPER | PWM GENERATOR x PERIOD REGISTER | PGxの周期を設定します |

| PGxPHASE | PWM GENERATOR x PHASE REGISTER | PGxの位相を設定します |

| PGxDC | PWM GENERATOR x DUTY CYCLE REGISTER | PGxのデューティを設定します |

| PGxDTH PGxDTL | PWM GENERATOR x DEAD-TIME REGISTER | PGxのデッドタイムを設定します |

| PGxEVTL PG1EVTH | PWM GENERATOR x Event REGISTER | PGxのイベントに関する設定を行います |

| PG1TRIGA PG1TRIGB | PWM GENERATOR x TRIGGER A REGISTER PWM GENERATOR x TRIGGER B REGISTER | PGxのトリガに関する設定を行います |

| DACCTRL1L | DAC CONTROL 1 LOW REGISTER | DAC制御1Lレジスタの設定 |

| DACCTRL2H | DAC CONTROL 2 HIGH REGISTER | DAC制御2Hレジスタの設定 |

| DACCTRL2L | DAC CONTROL 2 LOW REGISTER | DAC制御2Lレジスタの設定 |

| DACxCONH | DACx CONTROL HIGH REGISTER | DACx制御Hレジスタの設定 |

| DACxCONL | DACx CONTROL LOW REGISTER | DACx制御Lレジスタの設定 |

| DAC1DATH DAC1DATL | DACx DATA HIGH REGISTER DACx DATA LOW REGISTER | DACx値レジスタの設定 |

| SLP1CONH | DACx SLOPE CONTROL HIGH REGISTER | スロープx制御レジスタHレジスタの設定 |

| SLP1CONL | DACx SLOPE CONTROL LOW REGISTER | スロープx制御レジスタLの設定 |

| SLP1DAT | DACx SLOPE CONTROL LOW REGISTER | スロープxデータレジスタの設定 |

スロープ波形生成に大きく関わるレジスタは(fig.6)の通りです。

| レジスタ名 | 役割 |

| PG1PER | PWMの周期 |

| PG1DC | PWMのDuty |

| PG1TRIGA | スロープ開始タイミング |

| PG1TRIGB | スロープ終了タイミング |

| SLP1DAT | スロープ勾配 |

| DAC1DATH | スロープ開始電圧 |

| DAC1DATL | スロープ終了電圧 |

スロープ開始タイミングは以下の条件が真になった時に発生します。

1. タイムベース値がPG1TRIGAレジスタの値で決定します。

スロープ終了タイミングは以下3つのいづれかが真になった時に発生します。

1. タイムベース値がPG1TRIGBレジスタと一致した時

2. コンパレータなどのイベント発生時(今回は無効)

3. スロープ電圧がDAC1DATLに到達した時(負スロープの場合)

ソースコード

特に注意が必要なレジスタは以下のイベントレジスタの設定です。

上記の説明でスロープ開始/終了はTRIGA/Bレジスタと説明しましたが、正確ではありません。

イベントレジスタ(PGxEVTL)でTRIGAをTrig1に、TRIGBをTrig2に割り付ける必要が有ります。

/*TRIGAレジスタをTrig1とする*/

PG1EVTLbits.ADTR1EN1 = PWM_DRV_PGXEVTL_ADTR1EN1_ENABLE;

/*TRIGBレジスタをTrig2とする*/

PG1EVTHbits.ADTR2EN2 = PWM_DRV_PGXEVTH_ADTR2EN2_ENABLE;コンフィグレーション設定についてはコンフィグレーション設定に記載しております。

コピーして下記のソースコードの「 //ここにコンフィグレーション設定を挿入する// 」の位置に挿入してください。

クロック設定用関数 vds_Main_Init_Clock_Register(); のソースコードはクロック設定のページに記載しております。

コピーして下記のソースコードの「 //ここにクロック設定ソースをコピペする// 」の位置に挿入してください。

/*----------------------------------------------------------------------------*/

/* <Chapter> CHAPTER_2_7_5_HRPWM_SLOPE */

/* <Function> PWM1スロープ補償 */

/* <Peripharal> PWM関連 */

/*----------------------------------------------------------------------------*/

/*----------------------------------------------------------------------------*/

/* コンフィグレーション設定*/

/*----------------------------------------------------------------------------*/

//ここにコンフィグレーション設定を挿入する//

/*----------------------------------------------------------------------------*/

/* インクルードファイル*/

/*----------------------------------------------------------------------------*/

#include <stdio.h>

#include <stdlib.h>

#include <xc.h>

/*----------------------------------------------------------------------------*/

/* 定数定義*/

/*----------------------------------------------------------------------------*/

#define PWM_DRV_PGXEVTL_ADTR1EN1_DISABLE ( 0u) //PGxTRIGAレジスタコンペアイベントをADCトリガ1向け信号源として無効にする

#define PWM_DRV_PGXEVTL_ADTR1EN1_ENABLE ( 1u) //PGxTRIGAレジスタコンペアイベントをADCトリガ1向け信号源として無効にする

#define PWM_DRV_PGXEVTL_ADTR1EN2_DISABLE ( 0u) //PGxTRIGBレジスタコンペアイベントをADCトリガ1向け信号源として無効にする

#define PWM_DRV_PGXEVTL_ADTR1EN2_ENABLE ( 1u) //PGxTRIGBレジスタコンペアイベントをADCトリガ1向け信号源として無効にする

#define PWM_DRV_PGXEVTL_ADTR1EN3_DISABLE ( 0u) //PGxTRIGCレジスタコンペアイベントをADCトリガ1向け信号源として無効にする

#define PWM_DRV_PGXEVTL_ADTR1EN3_ENABLE 1u) //PGxTRIGCレジスタコンペアイベントをADCトリガ1向け信号源として無効にする

#define PWM_DRV_PGXEVTL_UPDTRG_MANUAL ( 0u ) //ユーザが手動でUPDREQビット(PGxSTAT<3>)をセットする必要がある

#define PWM_DRV_PGXEVTL_UPDTRG_PGXDC ( 1u ) //PGxDCレジスタの書き込み時に自動的にUPDREQビットをセットする

#define PWM_DRV_PGXEVTL_UPDTRG_PGXPHASE ( 2u ) //PGxPHASEレジスタの書き込み時に自動的にUPDREQビットをセットする

#define PWM_DRV_PGXEVTL_UPDTRG_PGXTRIGA ( 3u ) //PGxTRIGAレジスタの書き込み時に自動的にUPDREQビットをセットする

#define PWM_DRV_PGXEVTL_PGTRGSEL_EOC ( 0u ) //EOCイベントがPWMジェネレータトリガ

#define PWM_DRV_PGXEVTL_PGTRGSEL_PGXTRIGA ( 1u ) //PGxTRIGAコンペアイベントがPWMジェネレータトリガ

#define PWM_DRV_PGXEVTL_PGTRGSEL_PGXTRIGB ( 2u ) //PGxTRIGBコンペアイベントがPWMジェネレータトリガ

#define PWM_DRV_PGXEVTL_PGTRGSEL_PGXTRIGC ( 3u ) //PGxTRIGCコンペアイベントがPWMジェネレータトリガ

#define PWM_DRV_PGXEVTH_FLTIEN_DISABLE ( 0u ) //フォルト割り込み無効

#define PWM_DRV_PGXEVTH_FLTIEN_ENABLE ( 1u ) //フォルト割り込み有効

#define PWM_DRV_PGXEVTH_CLIEN_DISABLE ( 0u ) //電流制限割り込み無効

#define PWM_DRV_PGXEVTH_CLIEN_ENABLE ( 1u ) //電流制限割り込み有効

#define PWM_DRV_PGXEVTH_FFIEN_DISABLE ( 0u ) //フィードフォワード割り込み無効

#define PWM_DRV_PGXEVTH_FFIEN_ENABLE ( 1u ) //フィードフォワード割り込み有効

#define PWM_DRV_PGXEVTH_SIEN_DISABLE ( 0u ) //同期割り込み無効

#define PWM_DRV_PGXEVTH_SIEN_ENABLE ( 1u ) //同期割り込み有効

#define PWM_DRV_PGXEVTH_IEVTSEL_EOC ( 0u ) //EOC時にCPUに割り込む

#define PWM_DRV_PGXEVTH_IEVTSEL_TRIGA ( 1u ) //TRIGAコンペアイベント時にCPUに割り込む

#define PWM_DRV_PGXEVTH_IEVTSEL_ADC1 ( 2u ) //ADCトリガ1イベント時にCPUに割り込む

#define PWM_DRV_PGXEVTH_IEVTSEL_TB_DISABLE ( 3u ) //タイムベース割り込みを無効にする

#define PWM_DRV_PGXEVTH_ADTR2EN1_DISABLE ( 0u) //PGxTRIGAレジスタコンペアイベントをADCトリガ2向け信号源として無効にする

#define PWM_DRV_PGXEVTH_ADTR2EN1_ENABLE ( 1u) //PGxTRIGAレジスタコンペアイベントをADCトリガ2向け信号源として無効にする

#define PWM_DRV_PGXEVTH_ADTR2EN2_DISABLE ( 0u) //PGxTRIGBレジスタコンペアイベントをADCトリガ2向け信号源として無効にする

#define PWM_DRV_PGXEVTH_ADTR2EN2_ENABLE ( 1u) //PGxTRIGBレジスタコンペアイベントをADCトリガ2向け信号源として無効にする

#define PWM_DRV_PGXEVTH_ADTR2EN3_DISABLE ( 0u) //PGxTRIGCレジスタコンペアイベントをADCトリガ2向け信号源として無効にする

#define PWM_DRV_PGXEVTH_ADTR2EN3_ENABLE ( 1u) //PGxTRIGCレジスタコンペアイベントをADCトリガ2向け信号源として無効にする

#define DAC_DRV_DACCTRL1L_DACON_DISABLE ( 0u ) /* DAC モジュールを無効にする */

#define DAC_DRV_DACCTRL1L_DACON_ENABLE ( 1u ) /* DAC モジュールを有効にする */

#define DAC_DRV_DACCTRL1L_DACSIDL_CONTINUES ( 0u ) /* アイドル中もモジュールは動作を継続する */

#define DAC_DRV_DACCTRL1L_DACSIDL_STOP ( 1u ) /* デバイスがアイドルに移行した時にモジュールは動作を停止する */

#define DAC_DRV_DACCTRL1L_CLKSEL_AFVCODIV2 ( 0u )

#define DAC_DRV_DACCTRL1L_CLKSEL_FVCODIV2 ( 1u )

#define DAC_DRV_DACCTRL1L_CLKSEL_AFPLLO ( 2u )

#define DAC_DRV_DACCTRL1L_CLKSEL_FPLLO ( 3u )

#define DAC_DRV_DACCTRL1L_CLKDIV_1X1 ( 0u )

#define DAC_DRV_DACCTRL1L_CLKDIV_1X2 ( 1u )

#define DAC_DRV_DACCTRL1L_CLKDIV_1X3 ( 2u )

#define DAC_DRV_DACCTRL1L_CLKDIV_1X4 ( 3u )

#define DAC_DRV_DACCTRL1L_FCLKDIV_1X1 ( 0u )

#define DAC_DRV_DACCTRL1L_FCLKDIV_1X2 ( 1u )

#define DAC_DRV_DACCTRL1L_FCLKDIV_1X3 ( 2u )

#define DAC_DRV_DACCTRL1L_FCLKDIV_1X4 ( 3u )

#define DAC_DRV_DACCTRL1L_FCLKDIV_1X5 ( 4u )

#define DAC_DRV_DACCTRL1L_FCLKDIV_1X6 ( 5u )

#define DAC_DRV_DACCTRL1L_FCLKDIV_1X7 ( 6u )

#define DAC_DRV_DACCTRL1L_FCLKDIV_1X8 ( 7u )

#define DAC_DRV_DACXCONL_DACEN_DISABLE ( 0u ) /* DACxモジュールを無効にする */

#define DAC_DRV_DACXCONL_DACEN_ENABLE ( 1u ) /* DACxモジュールを有効にする */

#define DAC_DRV_DACXCONL_IRQM_DISABLE ( 0u ) /* 割り込みを無効にする */

#define DAC_DRV_DACXCONL_IRQM_RISING_EDGE ( 1u ) /* 立ち上がりエッジ検出時に割り込みを生成する */

#define DAC_DRV_DACXCONL_IRQM_FALLING_EDGE ( 2u ) /* 立ち下がりエッジ検出時に割り込みを生成する */

#define DAC_DRV_DACXCONL_IRQM_BOTH_EDGE ( 3u ) /* 立ち上がり / 立ち下がりエッジ検出時に割り込みを生成する */

#define DAC_DRV_DACXCONL_CBE_DISABLE ( 0u ) /* アナログコンパレータへのブランキング信号を無効にする */

#define DAC_DRV_DACXCONL_CBE_ENABLE ( 1u ) /* スロープ動作完了後の復帰遷移中にアナログコンパレータ出力のブランキング(停止)を有効にする */

#define DAC_DRV_DACXCONL_DACOEN_DISABLE ( 0u ) /* DACxアナログ電圧をDACOUT1ピンに接続しない */

#define DAC_DRV_DACXCONL_DACOEN_ENABLE ( 1u ) /* DACxアナログ電圧をDACOUT1ピンに接続する */

#define DAC_DRV_DACXCONL_FLTREN_DISABLE ( 0u ) /* デジタルフィルタを無効にする */

#define DAC_DRV_DACXCONL_FLTREN_ENABLE ( 1u ) /* デジタルフィルタを有効にする */

#define DAC_DRV_DACXCONL_CMPPOL_NORMAL ( 0u ) /* 出力を反転しない */

#define DAC_DRV_DACXCONL_CMPPOL_INVERT ( 1u ) /* 出力を反転する */

#if (CORE_TYPE == CORE_MASTER)

#define DAC_DRV_DACXCONL_INSEL_CMPXA ( 0u ) /* CMPxA 入力ピン */

#define DAC_DRV_DACXCONL_INSEL_CMPxB ( 1u ) /* CMPxB 入力ピン */

#define DAC_DRV_DACXCONL_INSEL_CMPxD ( 3u ) /* CMPxD 入力ピン */

#define DAC_DRV_DACXCONL_INSEL_SPGA1_OUT ( 4u ) /* SPGA1 出力 */

#define DAC_DRV_DACXCONL_INSEL_SPGA2_OUT ( 5u ) /* SPGA2 出力*/

#else

#define DAC_DRV_INSEL_S1CMPXA ( 0u ) /* S1CMPxA 入力ピン */

#define DAC_DRV_INSEL_S1CMPxB ( 1u ) /* S1CMPxB 入力ピン */

#define DAC_DRV_INSEL_S1CMPxD ( 3u ) /* S1CMPxD 入力ピン */

#define DAC_DRV_INSEL_SPGA1_OUT ( 4u ) /* SPGA1 出力 */

#define DAC_DRV_INSEL_SPGA2_OUT ( 5u ) /* SPGA2 出力*/

#endif

#define DAC_DRV_DACXCONL_HYSPOL_RISING_EDGE ( 0u ) /* 立ち下がりエッジにヒステリシスを適用する */

#define DAC_DRV_DACXCONL_HYSPOL_FALLING_EDGE ( 1u ) /* 立ち上がりエッジにヒステリシスを適用する */

#define DAC_DRV_DACXCONL_HYSSEL_NO ( 0u ) /* ヒステリシスを適用しない */

#define DAC_DRV_DACXCONL_HYSSEL_15MV ( 1u ) /* 15mVのヒステリシス */

#define DAC_DRV_DACXCONL_HYSSEL_30MV ( 2u ) /* 30mVのヒステリシス */

#define DAC_DRV_DACXCONL_HYSSEL_45MV ( 3u ) /* 45mVのヒステリシス */

#define DAC_DRV_SLPXCONH_SLOPEN_DISABLE ( 0u ) /* スロープ機能を無効にする */

#define DAC_DRV_SLPXCONH_SLOPEN_ENABLE ( 1u ) /* スロープ機能を有効にする */

#define DAC_DRV_SLPXCONH_HME_DISABLE ( 0u ) /* DACx のヒステリシス モードを無効にする */

#define DAC_DRV_SLPXCONH_HME_ENABLE ( 1u ) /* DACx のヒステリシス モードを有効にする */

#define DAC_DRV_SLPXCONH_TWME_DISABLE ( 0u ) /* DACx の三角波モードを無効にする */

#define DAC_DRV_SLPXCONH_TWME_ENABLE ( 1u ) /* DACx の三角波モードを有効にする */

#define DAC_DRV_SLPXCONH_PSE_DEC ( 0u ) /* スロープモードは負 ( 減少 ) */

#define DAC_DRV_SLPXCONH_PSE_ADD ( 1u ) /* スロープモードは正 ( 増加 ) */

#define DAC_DRV_SLPXCONL_HCFSEL_0 ( 0u ) /* 0 */

#define DAC_DRV_SLPXCONL_HCFSEL_PWM1H ( 1u ) /* PWM1H */

#define DAC_DRV_SLPXCONL_HCFSEL_PWM2H ( 2u ) /* PWM2H */

#define DAC_DRV_SLPXCONL_HCFSEL_PWM3H ( 3u ) /* PWM3H */

#define DAC_DRV_SLPXCONL_HCFSEL_PWM4H ( 4u ) /* PWM4H */

#define DAC_DRV_SLPXCONL_HCFSEL_S1PWM1H ( 5u ) /* S1PWM1H*/

#define DAC_DRV_SLPXCONL_HCFSEL_S1PWM2H ( 6u ) /* S1PWM2H */

#define DAC_DRV_SLPXCONL_HCFSEL_S1PWM3H ( 7u ) /* S1PWM3H */

#define DAC_DRV_SLPXCONL_HCFSEL_S1PWM4H ( 8u ) /* S1PWM4H*/

#define DAC_DRV_SLPXCONL_HCFSEL_1 ( 15u ) /* 1 */

#define DAC_DRV_SLPXCONL_SLPSTOPA_0 ( 0u ) /* 0 */

#define DAC_DRV_SLPXCONL_SLPSTOPA_PWM1TRG1 ( 1u ) /* Master PWM1 Trigger 1 */

#define DAC_DRV_SLPXCONL_SLPSTOPA_PWM2TRG1 ( 2u ) /* Master PWM2 Trigger 1 */

#define DAC_DRV_SLPXCONL_SLPSTOPA_PWM3TRG1 ( 3u ) /* Master PWM3 Trigger 1 */

#define DAC_DRV_SLPXCONL_SLPSTOPA_PWM4TRG1 ( 4u ) /* Master PWM4 Trigger 1 */

#define DAC_DRV_SLPXCONL_SLPSTOPA_PWM1TRG2 ( 5u ) /* Master PWM1 Trigger 2 */

#define DAC_DRV_SLPXCONL_SLPSTOPA_PWM2TRG2 ( 6u ) /* Master PWM2 Trigger 2 */

#define DAC_DRV_SLPXCONL_SLPSTOPA_PWM3TRG2 ( 7u ) /* Master PWM3 Trigger 2 */

#define DAC_DRV_SLPXCONL_SLPSTOPA_PWM4TRG2 ( 8u ) /* Master PWM4 Trigger 2 */

#define DAC_DRV_SLPXCONL_SLPSTOPA_S1PWM1TRG2 ( 13u ) /* Slave PWM1 Trigger 2 */

#define DAC_DRV_SLPXCONL_SLPSTOPA_S1PWM2TRG2 ( 14u ) /* Slave PWM2 Trigger 2 */

#define DAC_DRV_SLPXCONL_SLPSTOPA_1 ( 15u ) /* 1 */

#define DAC_DRV_SLPXCONL_SLPSTOPB_0 ( 0u ) /* 0 */

#define DAC_DRV_SLPXCONL_SLPSTOPB_CMP1 ( 1u ) /* CMP1 Out */

#define DAC_DRV_SLPXCONL_SLPSTOPB_S1CMP1 ( 2u ) /* S1CMP1 Out */

#define DAC_DRV_SLPXCONL_SLPSTOPB_S1CMP2 ( 3u ) /* S1CMP2 Out */

#define DAC_DRV_SLPXCONL_SLPSTOPB_S1CMP3 ( 4u ) /* S1CMP3 Out */

#define DAC_DRV_SLPXCONL_SLPSTOPB_1 ( 15u ) /* 1 */

#define DAC_DRV_SLPXCONL_SLPSTRT_0 ( 0u ) /* 0 */

#define DAC_DRV_SLPXCONL_SLPSTRT_PWM1TRG1 ( 1u ) /* Master PWM1 Trigger 1 */

#define DAC_DRV_SLPXCONL_SLPSTRT_PWM2TRG1 ( 2u ) /* Master PWM2 Trigger 1 */

#define DAC_DRV_SLPXCONL_SLPSTRT_PWM3TRG1 ( 3u ) /* Master PWM3 Trigger 1 */

#define DAC_DRV_SLPXCONL_SLPSTRT_PWM4TRG1 ( 4u ) /* Master PWM4 Trigger 1 */

#define DAC_DRV_SLPXCONL_SLPSTRT_PWM1TRG2 ( 5u ) /* Master PWM1 Trigger 2 */

#define DAC_DRV_SLPXCONL_SLPSTRT_PWM2TRG2 ( 6u ) /* Master PWM2 Trigger 2 */

#define DAC_DRV_SLPXCONL_SLPSTRT_PWM3TRG2 ( 7u ) /* Master PWM3 Trigger 2 */

#define DAC_DRV_SLPXCONL_SLPSTRT_PWM4TRG2 ( 8u ) /* Master PWM4 Trigger 2 */

#define DAC_DRV_SLPXCONL_SLPSTRT_S1PWM1TRG2 ( 13u ) /* Slave PWM1 Trigger 2 */

#define DAC_DRV_SLPXCONL_SLPSTRT_S1PWM2TRG2 ( 14u ) /* Slave PWM2 Trigger 2 */

#define DAC_DRV_SLPXCONL_SLPSTRT_1 ( 15u ) /* 1 */

/*----------------------------------------------------------------------------*/

/* 変数定義*/

/*----------------------------------------------------------------------------*/

/*----------------------------------------------------------------------------*/

/* クロック設定 */

/*----------------------------------------------------------------------------*/

//ここにクロック設定ソースを挿入する//

/*----------------------------------------------------------------------------*/

/* Main関数 */

/*----------------------------------------------------------------------------*/

int main(int argc, char** argv)

{

/*------------------------------------------------------------------------*/

/* クロック初期化*/

/*------------------------------------------------------------------------*/

vds_Main_Init_Clock_Register(); /* クロック初期化 */

/*------------------------------------------------------------------------*/

/* GPIO初期化*/

/*------------------------------------------------------------------------*/

ANSELBbits.ANSELB2 = 1u; /* RB2ピンはアナログピン(DACOUT1) */

/*------------------------------------------------------------------------*/

/* PWM初期化*/

/*------------------------------------------------------------------------*/

PG1CONLbits.ON = 0u;

/*------------------------------------------------------------------------*/

/* PWMクロックの設定*/

/*------------------------------------------------------------------------*/

PCLKCONbits.MCLKSEL = 3u; /* Auxiliary PLL post-divider output*/

/*------------------------------------------------------------------------*/

/* PGx制御レジスタLの設定*/

/*------------------------------------------------------------------------*/

PG1CONLbits.CLKSEL = 1u;

PG1CONLbits.MODSEL = 0u;

/*------------------------------------------------------------------------*/

/* PGx制御レジスタHの設定*/

/* 周期はマスターピリオドレジスタ(MPER)を使用*/

/*------------------------------------------------------------------------*/

PG1CONH = 0x0000;

/*------------------------------------------------------------------------*/

/* PGxIOレジスタHの設定*/

/* PWMジェネレータがピンを使用する*/

/*------------------------------------------------------------------------*/

PG1IOCONH = 0x000C;

/*------------------------------------------------------------------------*/

/* PGxIOレジスタLの設定*/

/* PCI電流リミットが発生した時にCLDATの値を使用*/

/* CLDAT = PWMxHがLow,PWMxLがHigh*/

/*------------------------------------------------------------------------*/

PG1IOCONL = 0x0010;

/*------------------------------------------------------------------------*/

/* 周期/Duty/フェーズの設定*/

/*------------------------------------------------------------------------*/

PG1PER = 4999;

PG1DC = 2999;

PG1PHASE = 0;

PG1TRIGA = 200;

PG1TRIGB = 2999;

/*------------------------------------------------------------------------*/

/* デッドタイムの設定*/

/*------------------------------------------------------------------------*/

PG1DTH = 10;

PG1DTL = 10;

/*------------------------------------------------------------------------*/

/* ブランキングの設定*/

/* PWMxHの立ち上がりでLEBカウンタをクリアする*/

/*------------------------------------------------------------------------*/

PG1LEBH = 0x0008u;

PG1LEBL = 200u;

/*------------------------------------------------------------------------*/

/* PCI電流制御レジスタHの設定*/

/*------------------------------------------------------------------------*/

PG1CLPCIH = 0x0300;

/*------------------------------------------------------------------------*/

/* イベントレジスタの設定*/

/*------------------------------------------------------------------------*/

PG1EVTL = 0x0118u;

PG1EVTLbits.ADTR1PS = 0u;

PG1EVTLbits.ADTR1EN3 = PWM_DRV_PGXEVTL_ADTR1EN3_DISABLE;

PG1EVTLbits.ADTR1EN2 = PWM_DRV_PGXEVTL_ADTR1EN2_DISABLE;

PG1EVTLbits.ADTR1EN1 = PWM_DRV_PGXEVTL_ADTR1EN1_ENABLE;

PG1EVTLbits.UPDTRG = PWM_DRV_PGXEVTL_UPDTRG_PGXTRIGA;

PG1EVTLbits.PGTRGSEL = PWM_DRV_PGXEVTL_PGTRGSEL_EOC;

PG1EVTH = 0x0340u;

PG1EVTHbits.FLTIEN = PWM_DRV_PGXEVTH_FLTIEN_DISABLE;

PG1EVTHbits.CLIEN = PWM_DRV_PGXEVTH_CLIEN_DISABLE;

PG1EVTHbits.FFIEN = PWM_DRV_PGXEVTH_FFIEN_DISABLE;

PG1EVTHbits.SIEN = PWM_DRV_PGXEVTH_SIEN_DISABLE;

PG1EVTHbits.IEVTSEL = PWM_DRV_PGXEVTH_IEVTSEL_TB_DISABLE;

PG1EVTHbits.ADTR2EN3 = PWM_DRV_PGXEVTH_ADTR2EN3_DISABLE;

PG1EVTHbits.ADTR2EN2 = PWM_DRV_PGXEVTH_ADTR2EN2_ENABLE;

PG1EVTHbits.ADTR2EN1 = PWM_DRV_PGXEVTH_ADTR2EN1_DISABLE;

PG1EVTHbits.ADTR1OFS = 0u;

/*------------------------------------------------------------------------*/

/* PWMの有効化*/

/*------------------------------------------------------------------------*/

PG1CONLbits.ON = 1u;

/*------------------------------------------------------------------------*/

/* DAC制御1Lレジスタの設定*/

/*------------------------------------------------------------------------*/

DACCTRL1L = 0x0000u;

DACCTRL1Lbits.DACON = DAC_DRV_DACCTRL1L_DACON_DISABLE;

DACCTRL1Lbits.DACSIDL = DAC_DRV_DACCTRL1L_DACSIDL_CONTINUES;

DACCTRL1Lbits.CLKSEL = DAC_DRV_DACCTRL1L_CLKSEL_AFVCODIV2;

DACCTRL1Lbits.CLKDIV = DAC_DRV_DACCTRL1L_CLKDIV_1X1;

DACCTRL1Lbits.FCLKDIV = DAC_DRV_DACCTRL1L_FCLKDIV_1X1;

/*------------------------------------------------------------------------*/

/* DAC制御2Hレジスタの設定*/

/*------------------------------------------------------------------------*/

DACCTRL2H = 0x8A;

/*------------------------------------------------------------------------*/

/* DAC制御2Lレジスタの設定*/

/*------------------------------------------------------------------------*/

DACCTRL2L = 0x55;

/*------------------------------------------------------------------------*/

/* DAC1制御Hレジスタの設定*/

/*------------------------------------------------------------------------*/

DAC1CONH = 0x0000u;

DAC1CONHbits.TMCB = 0;

/*------------------------------------------------------------------------*/

/* DAC1制御Lレジスタの設定*/

/*------------------------------------------------------------------------*/

DAC1CONL = 0x0000u;

DAC1CONLbits.DACEN = DAC_DRV_DACXCONL_DACEN_DISABLE;

DAC1CONLbits.IRQM = DAC_DRV_DACXCONL_IRQM_DISABLE;

DAC1CONLbits.CBE = DAC_DRV_DACXCONL_CBE_DISABLE;

DAC1CONLbits.DACOEN = DAC_DRV_DACXCONL_DACOEN_ENABLE;

DAC1CONLbits.FLTREN = DAC_DRV_DACXCONL_FLTREN_DISABLE;

DAC1CONLbits.CMPPOL = DAC_DRV_DACXCONL_CMPPOL_NORMAL;

DAC1CONLbits.INSEL = DAC_DRV_DACXCONL_INSEL_CMPXA;

DAC1CONLbits.HYSPOL = DAC_DRV_DACXCONL_HYSPOL_RISING_EDGE;

DAC1CONLbits.HYSSEL = DAC_DRV_DACXCONL_HYSSEL_NO;

/*------------------------------------------------------------------------*/

/* DAC値レジスタの設定*/

/*------------------------------------------------------------------------*/

DAC1DATH = 0xEFF;

DAC1DATL = 0x3FF;

/*------------------------------------------------------------------------*/

/* SLP制御レジスタHレジスタの設定*/

/*------------------------------------------------------------------------*/

SLP1CONH = 0x0000u;

SLP1CONHbits.HME = DAC_DRV_SLPXCONH_HME_DISABLE;

SLP1CONHbits.PSE = DAC_DRV_SLPXCONH_PSE_DEC;

SLP1CONHbits.TWME = DAC_DRV_SLPXCONH_TWME_DISABLE;

SLP1CONHbits.SLOPEN = DAC_DRV_SLPXCONH_SLOPEN_ENABLE;

/*------------------------------------------------------------------------*/

/* SLP制御レジスタLの設定*/

/*------------------------------------------------------------------------*/

SLP1CONL = 0x0000u;

SLP1CONLbits.HCFSEL = DAC_DRV_SLPXCONL_HCFSEL_0;

SLP1CONLbits.SLPSTOPA = DAC_DRV_SLPXCONL_SLPSTOPA_PWM1TRG2;

SLP1CONLbits.SLPSTOPB = DAC_DRV_SLPXCONL_SLPSTOPB_0;

SLP1CONLbits.SLPSTRT = DAC_DRV_SLPXCONL_SLPSTRT_PWM1TRG1;

/*------------------------------------------------------------------------*/

/* スロープデータレジスタの設定*/

/*------------------------------------------------------------------------*/

SLP1DAT = 50u;

DAC1CONLbits.DACEN = DAC_DRV_DACXCONL_DACEN_ENABLE; /* Enable Master DAC 1 */

DACCTRL1Lbits.DACON = DAC_DRV_DACCTRL1L_DACON_ENABLE; /* Turn ON all Master DACs */

/*------------------------------------------------------------------------*/

/* メインルーチン*/

/*------------------------------------------------------------------------*/

while(1)

{

}

}結果

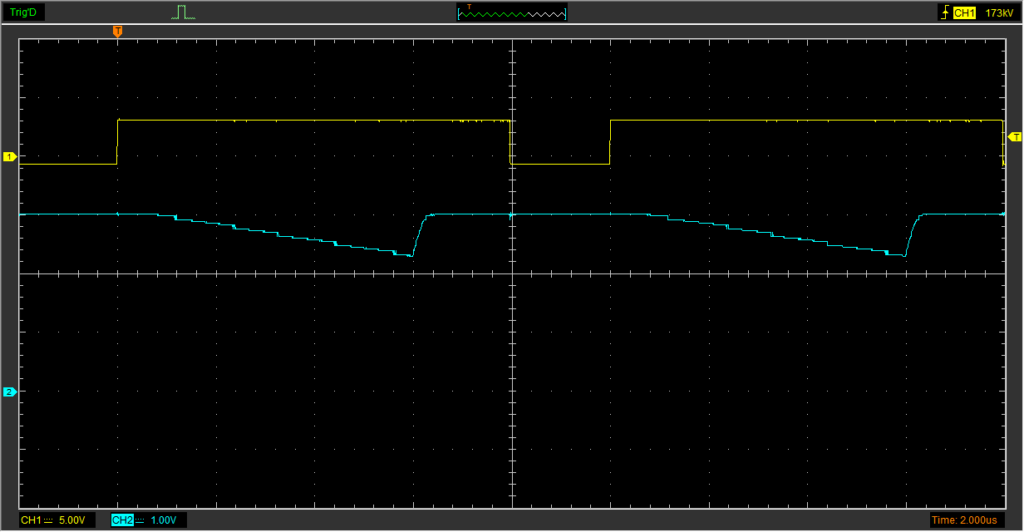

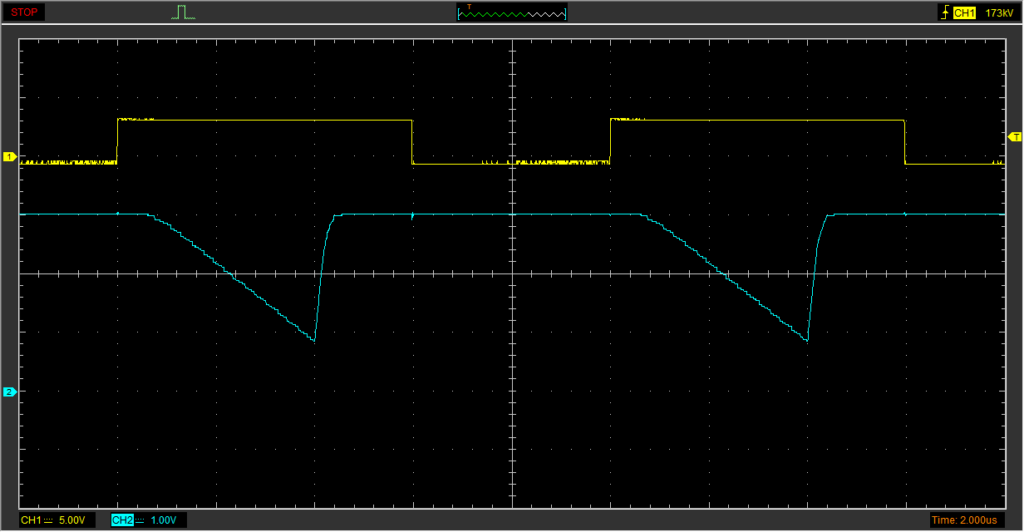

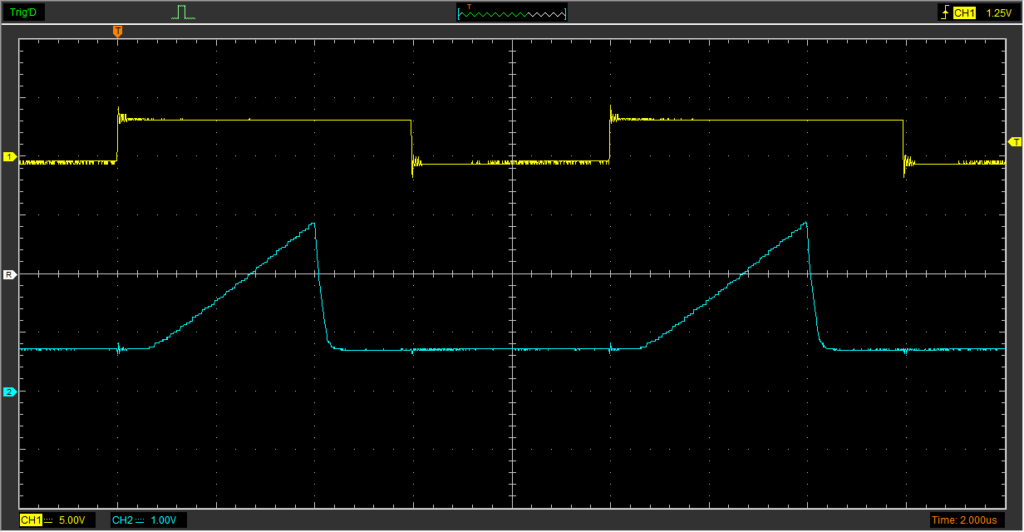

(fig.8)(fig.9)に示すように、PWMと同期したスロープ信号が生成されている事が確認できます。

また SLP1CONHbits.PSE を 1に設定すると、スロープ方向が変化します。

コメント